|

TwojePC.pl © 2001 - 2024

|

|

RECENZJE | Technika. Droga ku wydajności |

|

| |

|

Technika. Droga ku wydajności

Autor: Zbyszek | Data: 23/04/07

| |

|

1995 - rok procesorowych rewolucji

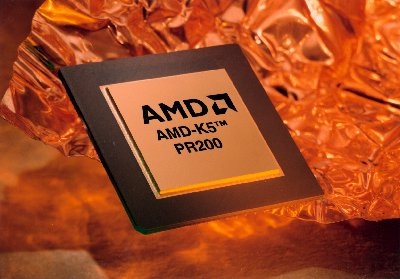

Na początku 1995 roku pojawił się procesor AMD K5, będący odpowiedzią na procesor Intel Pentium i pierwszym w historii układem stworzonym przez AMD, firmę dotychczas produkującą różne odmiany Intelowskich układów 386 i 486.

W Praktyce K5 nie był w pełni własną konstrukcją AMD - powstał poprzez zmodyfikowanie układu NextGEN, przejętego przez AMD wraz z całą firmą.

Już w czasach K5 AMD stosowało oznaczenia wydajności Performance Rating ( PR ) współcześnie znane z procesorów Athlon 64. Widoczny na zdjęciu K5 wydajnością

odpowiadał Pentium 200MHz, pracując z niższą od niego częstotliwością.

W K5 zastosowano nowatorską technikę, polegającą na przekodowywaniu wewnątrz układu instrukcji x86, na mikroinstrukcje wewnętrznego kodu procesora. Instrukcje x86 będące złożonymi instrukcjami o zmiennej długości, przekodowywane były na prostsze mikroinstrukcje o stałej długości, a te z kolei przeznaczone były do dalszego wykonywania w potokach układu. Przeciętnie jedna markoinstrukcja x86, tłumaczona była na 2-3 mikroinstrukcje wewnętrzne procesora.

Dodatkowo nad procesem przekodowywania instrukcji, czuwał specjalnie stworzony do tego celu kompilator, który w drodze przekodowywania ciągu instrukcji, mógł dokonać na nim pewnych optymalizacji, zastępując najbardziej niewygodne rozkazy zestawem innych instrukcji. Oczywiście wszystko to w pewnych granicach, by nie zmienić programu. To było by niedopuszczalne.

Poza jednym - zdecydowano wówczas by na drodze procesu przekodowywania, pominąć oprócz rozkazów odczytu i zapisu ( Load i Store ) wszystkie pozostałe instrukcje bezpośrednio odwołujące się do lokacji w pamięci operacyjnej, i w ogóle nie uwzględniać ich w przetwarzanym w potokach wewnętrznych mikrokodzie. Wyeliminowało to przynoszące ogromne straty wydajności instrukcje, wstrzymujące potoki wykonawcze na kilkaset cykli zegara - problem bardzo komplikujący potokowe przetwarzanie kodu x86.

Tak drastyczna zmiana nie mogła jednak obejść się bez konsekwencji. Wyeliminowane instrukcje były przecież wykorzystywane przez programy. Efekt: znaczna część programów nie działała poprawnie na K5. Konieczne było czasochłonne przepisanie aplikacji od nowa, bez uwzględniania w nich tychże instrukcji. Na AMD posypały się gromy, a sam procesor cieszył się bardzo niewielkim powodzeniem. Powszechne było całkowicie błędne stwierdzenie, że firma ta nie jest w stanie stworzyć poprawnie działającego układu. Jednak ktoś, kto wiedział, czym spowodowany został taki fakt rzeczy, dostrzegał w tym ogromny krok milowy.

Gdyby nie ówczesne poświęcenie AMD, współczesne procesory mogłyby po dziś dzień "męczyć się" z instrukcjami bezpośrednio odwołującymi się do pamięci operacyjnej. Intel mający w pamięci błędy, i niedawną wymianę dużych ilości procesorów Pentium, mógłby nie zdecydować się na wprowadzenie tak drastycznego, ale koniecznego posunięcia w swoich przyszłych procesorach.

Dziś, na szczęście, można tylko domniemywać jak duży spadek wydajności współczesnych CPU spowodowałaby dalsza konieczność wykonywania instrukcji odwołujących się do lokacji w pamięci RAM, a jeżeli jakiś programista umieści takie, dawniej powszechnie stosowane instrukcje w swoim programie, będzie to tylko i wyłącznie jego błąd.

|

|

|

|

|

|

|

|

|

|