|

TwojePC.pl © 2001 - 2026

|

|

RECENZJE | Technika. Droga ku wydajności |

|

| |

|

Technika. Droga ku wydajności

Autor: Zbyszek | Data: 23/04/07

| |

|

Wydajny RISC

Wprowadzenie etapowego potoku wykonawczego dało w efekcie wydajność bliską jednej instrukcji na cykl zegara - nieosiągalną dla procesorów CISC, które na wykonanie jednego rozkazu potrzebowały przeciętnie od kilkunastu, do nawet kilkuset taktów zegara w przypadku bardzo złożonych instrukcji.

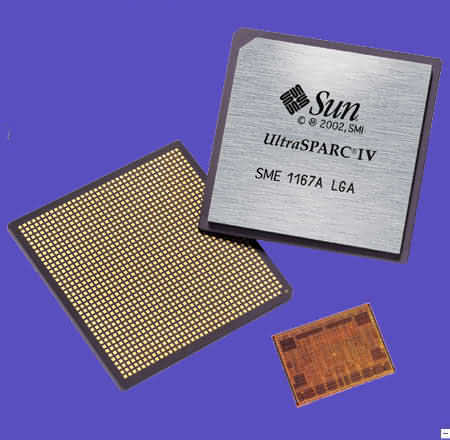

Układy x86 przejmują od swoich RISCowych krewnych nie tylko rozwiązania wewnętrznej budowy. Widoczny na zdjęciu układ Sun UltraSparc 4 korzystał z obudowy LGA na długo przed tym, gdy pojawiły się pierwsze Pentium 4 wykorzystujące to rozwiązanie.

Ale to nie wszystkie korzyści, jakie przyniosła architektura potokowa wespół z ideologią RISC. Zredukowanie złożoności instrukcji, oraz podzielenie procesu ich wykonywania na kilka mniej skomplikowanych etapów sprawiło, że poszczególne etapy stały się prostsze, przez co dawały się wykonać w mniejszych przedziałach czasu. Krótsze czasy wykonywania pojedynczych etapów spowodowały, że takty zegara procesora mogły następować po sobie w krótszych odstępach czasu.

Jakieś korzyści? - możliwość kilkukrotnego zwiększenia taktowania CPU!

Kilkakrotnie szybciej taktowany procesor, pracujący nad kilkoma instrukcjami jednocześnie w ramach jednego strumienia instrukcji. Nie trudno wyobrazić sobie skalę przyśpieszenia w stosunku do procesorów CISC dysponujących przetwarzaniem prostym.

Jednak czy coś stało na przeszkodzie, aby w procesorze RISC potoków wykonawczych było więcej niż jeden? Budowa instrukcji, na których operowały układy RISC, przystosowanych do równoległego wykonywania, aż prosiła się o zastosowanie takiego rozwiązania.

|

|

|

Rozdziały: Technika. Droga ku wydajności |

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|