Conroe - niebieska kontra, czyli test procesora Intel Core 2 Duo

Autor: Lancer | Data: 11/09/06

| |

|

W stronę sukcesu

Ponieważ rozwijane równolegle z P6 jądro P5 wyczerpało możliwości dalszej ewolucji, Intel kolejne swe projekty oparł właśnie o rdzeń P6, który ciągle miał wielkie możliwości rozwoju.

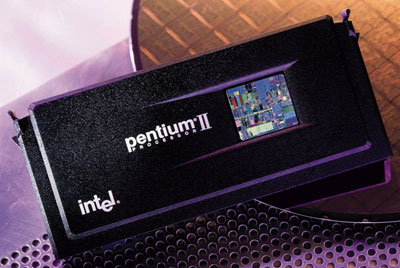

Pentium II oparty na architekturze Pentium Pro i używał zewnętrznego cache L2, Nie był on zintegrowany jak poprzednio, ale umieszczony na zewnątrz rdzenia, choć wciąż na wspólnej z rdzeniem płytce drukowanej łączonej z płytą główną złączem krawędziowym Slot 1. Do tego moduły pamięci pracowały już tylko z połową prędkości rdzenia i miały pojemność 512KB. Pozwalało to uzyskiwać procesory niższym kosztem, jednocześnie zachowując stosunkowo wysoką prędkość komunikacji jądra z pamięcią podręczną. Układ nie musiał bowiem do tego celu używać szyny FSB jak miało to miejsce w procesorach Pentium (także Pentium MMX), korzystających z pamięci umieszczonej na płycie głównej, a używał do tego dedykowanej szyny BSB służącej tylko do komunikacji z cache drugiego poziomu. Podwojono wielkość pamięci cache L1, na którą składały się dwa 16KB bloki (jeden na dane i jeden na instrukcje) zmniejszając tym samym częstość odwołań do wolniejszej niż w Pentium Pro cache L2. Uczyniono też kroki mające wyeliminować podstawową wadę Pentium Pro - poprawić zdolność przetwarzania 16-bitowego kodu przez dodanie pamięci podręcznej rejestrów segmentowych. Pentium II odziedziczył też co nieco z rdzenia P55C - 57 instrukcji SIMD MMX. To tyle nowości.

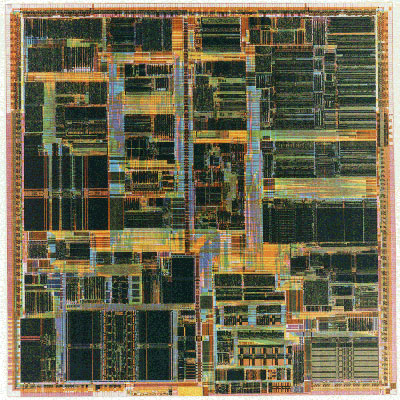

Struktura krzemowa rdzenia Klamath

Wielkich zmian w czasie swojej trzyletniej produkcji procesor nie zaznał. Zmieniono tylko proces technologiczny z początkowego 350nm na 250nm. Przyspieszeniu uległa także szyna GTL+ odziedziczona po Pentium Pro z 66 do 100MHz.

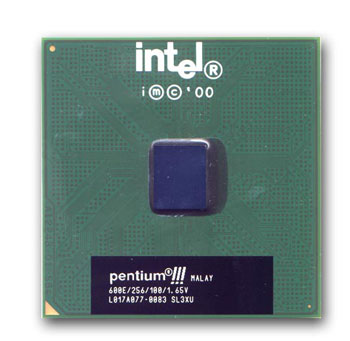

Pentium II w obudowie SEC

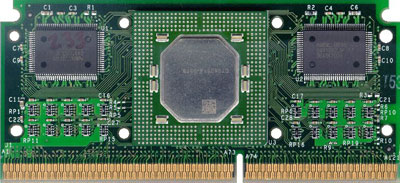

Pentium II z rdzeniem Klamath bez obudowy. Widoczne 4 moduły pamięci podręcznej SRAM i bufor znaczników TagRAM

Ten sam procesor od przodu

W takiej formie rdzeń P6 przetrwał dosyć długo. Na poważniejszy lifting przyszło czekać aż do trzeciej generacji układów Pentium. Najpierw wraz z 250nm rdzeniem Katmai procesor doczekał się rozszerzenia SIMD w postaci 70 instrukcji SSE realizowanych przez dwa kanały z ośmioma 128-bitowymi rejestrami operującymi na liczbach zmiennoprzecinkowych pojedynczej precyzji. Pojawiło się także 12 kolejnych instrukcji starszego typu - MMX. Co ważne nowe rejestry SSE umożliwiły równoległe używanie jednostek stałoprzecinkowych FP (na których operuje MMX) i jednostki zmiennoprzecinkowej podwójnej precyzji. Pomniejsze zmiany dotyczyły usprawnień w przepływie danych w procesorze i usprawnień w zarządzaniu podręczną pamięcią cache.

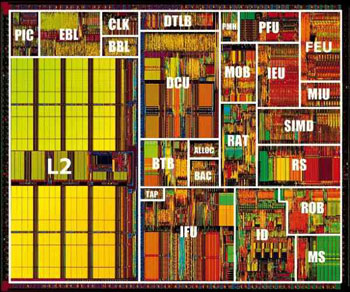

Struktura rdzenia Katmai

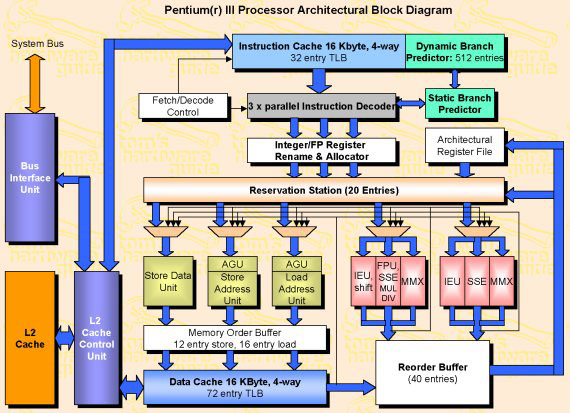

Schemat działania Pentium !!!

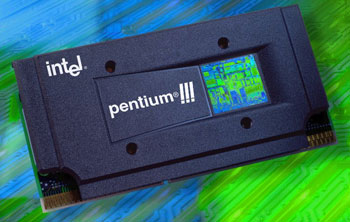

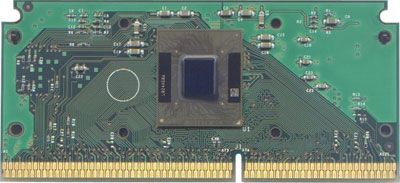

Pentium!!! Slot 1 w obudowie typu SEC2

W późniejszym okresie, wraz z 180nm jądrem Coppermine cache L2 powrócił powrotem do rdzenia. Intel walcząc z istotną nowinką na rynku, procesorami K7 powrócił więc do idei, która stanowiła ważną cechę pierwotnej wersji architektury P6. Cache jakkolwiek mający tylko 256KB pojemności pracował z pełną prędkością rdzenia i stanowił jedność z krzemową strukturą rdzenia. Co więcej komunikacja z pamięcią odbywała się szeroką 256-bitową, ośmiodrożną szyną. Szybka, oferująca nie tylko wysoką przepustowość, ale i niskie opóźnienia pamięć nazwano Advanced Transfer Cache. Do rdzenia wprowadzono też kilka pomniejszych zmian jak choćby powiększenie o połowę liczby buforów szyny FSB (fill buffers) i zwielokrotnienie buforów zapisu (typu write back).

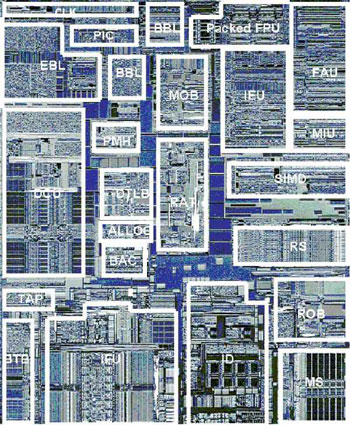

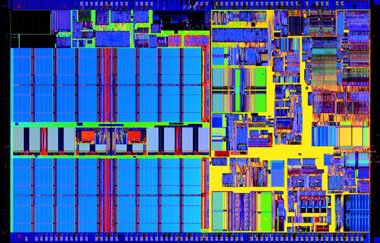

Rdzeń Coppermine z wyszczególnionymi blokami jednostek wykonawczych

P!!! Coppermine w wersji na gniazdo Slot1...

... i w obudowie FCPGA dla gniazda Socket 370

Ostatnim rodowitym procesorem Pentium !!! był Tualatin - wyposażony w 256 lub 512kb cacheL2 układ wykonany w 130nm procesie technologicznym, używający miedzianych ścieżek. Jedyną innowacją było dodanie systemu pobrań wyprzedzających (Data Cache Prefetch).

Rdzeń Tualatin – widoczny z lewej strony duży, 512KB blok pamięci podręcznej

Pentium !!! S z rdzeniem Tualatin

|

|

|

Rozdziały: Conroe - niebieska kontra, czyli test procesora Intel Core 2 Duo |

|

| |

|

|

|

|

|

|

|

|