Conroe - niebieska kontra, czyli test procesora Intel Core 2 Duo

Autor: Lancer | Data: 11/09/06

| |

|

Banias do kwadratu

Ostatnim etapem ewolucji P6 przed pojawieniem się Conroe jest rdzeń 65nm Yonah, który na rynku występuje pod nazwą handlową Core Duo i jest pierwszym od wielu lat masowym procesorem Intela x86, który nie używa zarzuconej nazwy Pentium. Nowy układ nie mógł bowiem kojarzyć się z energochłonnym Pentium 4 NetBurst i miał stanowić zapowiedź kolejnych procesorów odchodzących od tej architektury i dających początek czemuś nowemu. Mimo to Yonah wciąż jest procesorem mobilnym, ale dzieli go już tylko krok do Conroe.

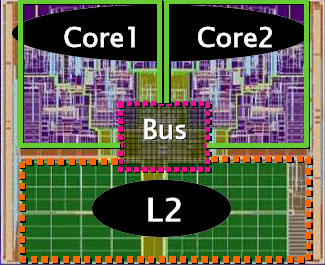

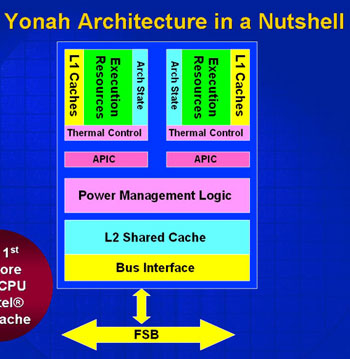

Podstawową różnicą między dotychczasowymi produktami serii Pentium M, a Yonahem jest wielordzeniowość. Procesor posiada dwa rdzenie korzystające ze wspólnej, integralnej 2MB pamięci podręcznej (Smart Cache). Jest to rozwiązanie dokładnie odwrotne w stosunku do spotykanej powszechnie architektury dwurdzeniowych układów Athlon 64 X2 i Pentium D.

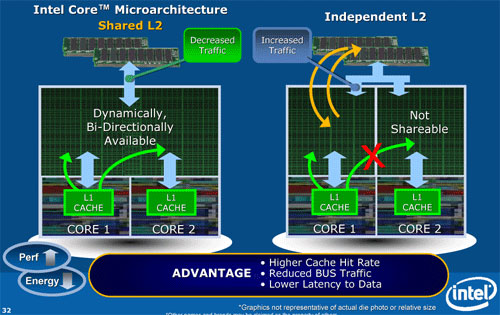

Schemat logiczny dwurdzeniowego procesora z niezależnym cache L2 dla każdego rdzenia

Architektura rdzenia Yonah i ze współdzielonym cache L2

Wspólna pamięć podręczna daje wiele korzyści. Przede wszystkim rozwiązuje problem od wielu lat trapiący rozwiązania wieloprocesorowe – spójności danych cache L2. Dlaczego to zagadnienie jest tak ważne? Układy korzystające z niezależnych pamięci podręcznych muszą uzgadniać zawartość cache, stosując system zachowania spójności cache. Rdzeń (procesor), który wykonał operację musi przesłać odpowiednią informację do drugiego rdzenia (procesora) podejmującego kolejne działanie informując o tym, że dane na których operował uległy modyfikacji. Drugi rdzeń musi po prostu operować na zmodyfikowanych przez pierwszy rdzeń danych. Procedura taka wymaga przesłania zawartości pamięci pomiędzy układami. Blokuje to na pewien czas dostęp do szyny FSB, aż do czasu zakończenia transmisji. Traconych jest na to kilkanaście cykli procesora. Yonah nie musi marnować czasu na uzgadnianie zawartości cache pomiędzy rdzeniami, jako że oba mają dostęp do tych samych danych umieszczonych we wspólnej pamięci. To oczywiście nie koniec zalet. W zadaniach jednowątkowych, gdy obliczeniami zajęty jest tylko jeden z rdzeni - drugi pozostaje bezczynny, aktywny układ może korzystać z pełnej pojemności pamięci cache przydzielając dla swoich potrzeb całe 2MB cache. Jedna, wspólna pamięć upraszcza konstrukcje procesora, ogranicza ilość pobieranej i wydzielanej energii - co dla układu mobilnego jest bardzo ważne. Znacznie obciążona w chipach wielordzeniowych szyna FSB nie musi już tracić cennej przepustowości na uzgadnianie spójności pamięci podręcznej rdzeni, a procesor również nie musi czekać na wynik tego działania. Strata wynikająca z konieczności uzgodnienia zawartości cache w przypadku dwurdzeniowych Athlonów 64 X2 wynosi 110ns, podczas gdy dla Pentium D jest to aż 200ns.

Niestety nic nie jest idealne. Znacznemu wydłużeniu w stosunku do wcześniejszych mutacji P6 uległ czas dostępu do pamięci podręcznej. Dzieje się tak m.in. dlatego, że w tym samym czasie dostęp do pamięci ma tylko jeden z rdzeni. Komunikacja z cache L2 odbywa się więc w sposób naprzemienny. Jednak wadę tą w znacznym stopniu niweluje szeroka ścieżka dostępowa do pamięci, znacząco skracająca czas potrzebny na przesłanie danych i unieruchamiająca jedno z jąder. W przypadku rdzenia Coopermine latencja pomięci podręcznej wynosiła około 7 cykli, Baniasa 9, a Dothana 10 cykli, to w przypadku Yonaha mamy już 14-15 cykli.

Kolejny raz w Yonahu przeprojektowano jednostkę pre-odczytu (Prefetch). Jej rola jest bardzo ważna, bowiem odpowiada teraz za dostarczanie do pamięci podręcznej danych wykorzystywanych już nie przez jeden, a dwa rdzenie. Trafność tego mechanizmu musi być więc wyjątkowo wysoka. Niejako przy okazji przeglądowi poddano bufory zapisu, które mają teraz większą głębokość.

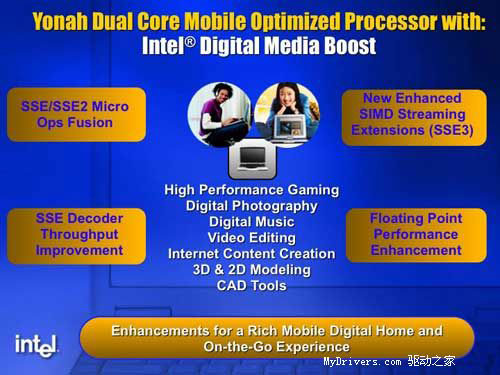

Dodanie drugiego jądra i zmiana roli pamięci cache L2 to ważne cechy wyróżniające procesor na tle Dothana, ale nie jedyne. Yonah wzbogacił się o 13 znanych z Prescotta instrukcji SSE3, ale jednocześnie przyspieszeniu uległy operacje na instrukcjach SSE. Znacznie wyższą wydajność pracy uzyskano dzięki zaprzęgnięciu wszystkich trzech dekoderów instrukcji. Operacje SIMD na rozszerzeniach SSE mogą być łączone dzięki mechanizmowi Micro Ops Fusion. Przyspieszeniu uległy też operacje przeprowadzane na jednostkach zmiennoprzecinkowych (Floating Point Unit), które od czasu pierwszych procesorów Pentium nie uległy poważniejszym modernizacjom. Wszelkie zmiany wokół mechanizmów odpowiedzialnych za jednostki FP i SSE zostały nazwane Intel Digital Media Boost ze względu na ich główną przydatność w szeroko rozumianych zastosowaniach multimedialnych.

Funkcjonalność procesora powiększyła obsługa wirtualizacji Intel Virtualization Technology skrywana pod kodową nazwą Vanderpool. Z wydajnościowego punktu widzenia warte nadmienienia jest kolejne podniesienie taktowania szyny FSB do 166MHz (667MHz QPB).

W Yonahu Znacznej rozbudowie uległy mechanizmy oszczędzania energii. Podstawą działania funkcji jest zmiana stanu pracy procesora. Normalnym trybem pracy jest stan wyłączenia jednostek chyba, że są potrzebne do pracy i dopiero wtedy są one aktywowane. Dzieje się to w zgodności z protokołem „Normaly Off”. W dotychczasowych rdzeniach trybem podstawowym był stan dokładnie odwrotny tj. „Normaly On” - gdy niepotrzebne jednostki były dopiero specjalnie wyłączane dla oszczędzania energii. Samo tylko odwrócenie trybu pracy bloków wykonawczych pozwala zmniejszyć zapotrzebowanie energetyczne o około 7%.

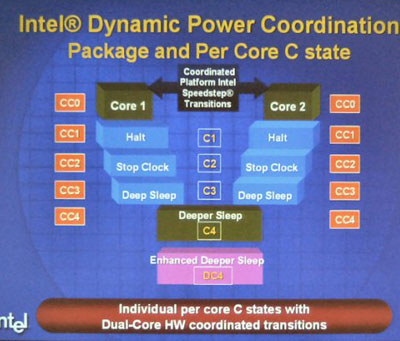

Yonah i jego 6 stanów aktywności

Na tym nie koniec. Yonah udostępnia znacznie bardziej rozbudowane niż Banias/Dothan stany aktywności. Istniejące już wcześniej, a oznaczone C0, C1, C2, C3, C4 tryby zostały wzbogacone o kolejny stan - DC4, w którym to, poza wyłączeniem bloków procesora, obniżeniem zegara i napięcia zasilającym (stan głębokiego uśpienia) następuje całkowite wyczyszczenie i wyłączenie cache L2 z przeniesieniem jej zawartości do wydzielonego obszaru pamięci operacyjnej. Kolejny zysk dało uniezależnienie od siebie pracy każdego z dwóch rdzeni. Dano możliwość zmiany trybu aktywności każdego z nich osobno w zależności od obciążenia. W chwili wykonywania zadań jednowątkowych drugi rdzeń przechodzi do niższego stanu aktywności jeśli tylko nie jest potrzebny w danej chwili. Kiedy aktywny jest jeden tylko rdzeń (stan CC0), drugi może uzyskać stan C3 Deep Sleep. Dwa najbardziej oszczędne tryby (CC4 Deeper Sleep i DC4 Enhanced Deeper Sleep) mogą być ustanowione tylko dla dwóch rdzeni jednocześnie, a więc w chwili braku obciążenia dla całego procesora. Oczywiście dalej istnieje możliwość selektywnego wyłączania poszczególnych bloków pamięci cache L2 w zależności od aktualnych potrzeb wykonywanej aplikacji, jeśli ta nie wymaga zajęcia całej dostępnej przestrzeni pamięci podręcznej. Mechanizm nadzorujący i realizujący wszystkie poszczególne stany energetyczne rdzeni zyskał nazwę DPC (Dynamic Power Coordination).

Procesor Core Duo Yonah. Widoczny zmieniony w stosunku do Dothana kształtu rdzenia

|

|

|

Rozdziały: Conroe - niebieska kontra, czyli test procesora Intel Core 2 Duo |

|

| |

|

|

|

|

|

|

|

|