|

TwojePC.pl © 2001 - 2025

|

|

Poniedziałek 16 czerwca 2025 |

|

| |

|

Tak wygląda przyszłość pamięci HBM

Autor: Wedelek | 06:56 |

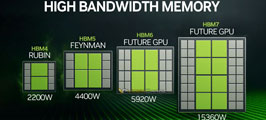

|  Podczas prezentacji KAIST Memory Systems Laboratory i TERA Interconnection and Packaging Group zaprezentowała nowy plan rozwoju High Bandwidth Memory (HBM). Plan obejmuje rozwój kolejnych pięciu generacji, HBM4 do HBM8 włącznie. Z każdą kolejną iteracją mamy zobaczyć wyraźny postęp w dziedzinie wydajności i przepustowości. Pierwsza z opisywanych generacji, czyli HBM4 trafi do akceleratorów AI i GPU dla centrów danych już w 2026 roku. Oferować będzie około przepustowość na poziomie 2 TB/s na stos - 8 Gb/s na pin przy 2048-bitowym interfejsie. Podczas prezentacji KAIST Memory Systems Laboratory i TERA Interconnection and Packaging Group zaprezentowała nowy plan rozwoju High Bandwidth Memory (HBM). Plan obejmuje rozwój kolejnych pięciu generacji, HBM4 do HBM8 włącznie. Z każdą kolejną iteracją mamy zobaczyć wyraźny postęp w dziedzinie wydajności i przepustowości. Pierwsza z opisywanych generacji, czyli HBM4 trafi do akceleratorów AI i GPU dla centrów danych już w 2026 roku. Oferować będzie około przepustowość na poziomie 2 TB/s na stos - 8 Gb/s na pin przy 2048-bitowym interfejsie.

Stosy krzemowe będą miały od 12 do 16 warstw, zapewniając 36–48 GB na pakiet przy poborze mocy 75 W. NVIDIA Rubin i AMD Instinct MI500 jako pierwsze wykorzystają HBM4, przy czym Rubin Ultra podwoi liczbę stosów pamięci do szesnastu, a AMD planuje nawet 432 GB na urządzenie.

W 2029 roku pojawi się HBM5 z przepustowością 8 Gb/s na pin, ale podwajając liczbę linii I/O do 4096, co pozwoli osiągnąć dwukrotnie wyższą przepustowość (4 TB/s) na stos. Pojemność pamięci wzrośnie do 80 GB (16-warstwowe stosy z kośćmi 40 Gb), a pobór mocy do 100 W. Pierwszym akceleratorem z HBM5 ma być Feynman od Nvidii. Karta ta mieć 400–500 GB pamięci i pobierać ponad 4400 W.

Około 2032 roku pojawi się HBM6, który podwoi przepustowość do 16 Gb/s na interfejs i do 8 TB/s na stos. Przy tym wysokość stosu wzrośnie do 20 warstw, co da 120 GB przy 120 W. W tym czasie standardem stanie się chłodzenie zanurzeniowe i połączenia miedź-miedź bez wyprowadzeń. W 2035 roku HBM7 zaoferuje przepustowość 24 Gb/s, 8192-bitowy interfejs, co da 24 TB/s na stos, który ma oferować do 192 GB pojemności przy TDP 160W.

|

| |

|

|

|

|

|

|

|

|

|

|

D O D A J K O M E N T A R Z |

|

| |

|

Aby dodawać komentarze, należy się wpierw zarejestrować, ewentualnie jeśli posiadasz już swoje konto, należy się zalogować.

|

|

|

|

|

|

|

|

|

|