|

TwojePC.pl © 2001 - 2026

|

|

Piątek 5 czerwca 2020 |

|

| |

|

Intel opracował nowy zestaw instrukcji usprawniających działanie cache

Autor: Wedelek | źródło: Tech Power Up | 21:59 |

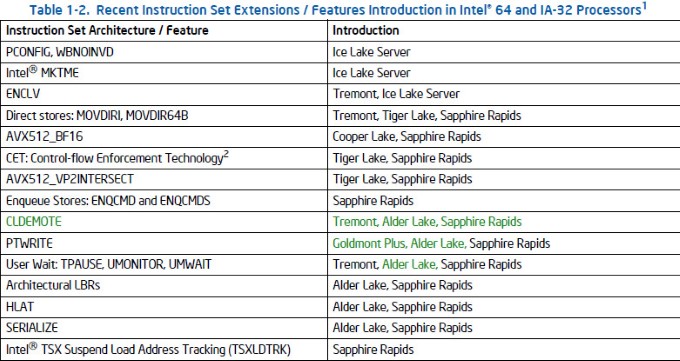

(11) |  Intel opracował nowy zestaw instrukcji dla swoich przyszłych procesorów, który ma za zadanie usprawnić działanie pamięci podręcznej. Nosi on nazwę CLDEMOTE i jest to skrót od sformułowania cache line demote. Jak sama nazwa wskazuje, zadaniem nowych instrukcji jest przenoszenie danych pomiędzy różnymi poziomami pamięci podręcznej w momencie zmiany priorytetu w dostępie do nich. Przykładowo, korzystając z CLDEMOTE określona porcja informacji będzie mogła być przeniesiona z pamięci podręcznej L2 do znacznie pojemniejszej, ale i wolniejszej L3 bez konieczności angażowania pamięci RAM. Intel opracował nowy zestaw instrukcji dla swoich przyszłych procesorów, który ma za zadanie usprawnić działanie pamięci podręcznej. Nosi on nazwę CLDEMOTE i jest to skrót od sformułowania cache line demote. Jak sama nazwa wskazuje, zadaniem nowych instrukcji jest przenoszenie danych pomiędzy różnymi poziomami pamięci podręcznej w momencie zmiany priorytetu w dostępie do nich. Przykładowo, korzystając z CLDEMOTE określona porcja informacji będzie mogła być przeniesiona z pamięci podręcznej L2 do znacznie pojemniejszej, ale i wolniejszej L3 bez konieczności angażowania pamięci RAM.

To powinno usprawnić funkcjonowanie całego podsystemu pamięci i w konsekwencji pozytywnie wpłynąć na wydajność całego procesora. Pierwszymi układami, które maja korzystać z CLDEMOTE będą serwerowe Sapphire Rapids, przeznaczone dla średniej półki cenowej chipy Alder Lake oraz niskonapięciowe Atomy, Pentiumy i Celerony na bazie rdzeni x86 Tremont.

|

| |

|

|

|

|

|

|

|

|

|

|

K O M E N T A R Z E |

|

| |

|

- mam nadzieję że nowe instrukcję oprócz usprawnienia podsystemu mem (autor: Qjanusz | data: 5/06/20 | godz.: 22:16)

usprawni też coś w kwestii bezpieczeństwa.

Inna sprawa... byłem przekonany że wymiana informacji pomiędzy poziomami cache, we wszystkich CPU odbywa się bezpośrednio, bez udziału RAMu. Wydaje się to oczywiste, a tutaj proszę, Intel taką oczywistość właśnie dopiero odkrył.

- @ Qjanusz (autor: Zbyszek.J | data: 5/06/20 | godz.: 23:25)

to zależy od architektury. Są pamięci cache inclusive i exclusive. Cache L2 tupu inclusive zawiera w sobie kopię cache L1. Cache L3 Inclusive zawiera w sobie kopie L2 (wraz z kopią L1, jeśłi L2 jest też inclusive).

Np. w Skylake (standardowym) cache L3 (2MB / rdzeń) jest typu inclusive i zawiera kopię 256 Kb cache L2. W skylake-X cache L3 (1,375 MB na rdzeń) jest typu exclusive i nie zawiera kopii cache L2 (1MB na rdzeń).

W x86 znacznie przeważają pamięci cache typu Inclusive. Cache Exclusive ma wyższą pojemność efektywną, ale tą słabość, że przenoszenie danych z L2 do L3 (czy z L1 do L2) trwa dłużej. Instrukcja CLDEMOTE jak rozumiem rozwiązuje ten problem.

- uzupełniając (autor: Zbyszek.J | data: 5/06/20 | godz.: 23:35)

w cache typu inclusive kopiowanie pomiędzy pamięciami odbywa się bez udziału RAM

- @Zbyszek.J (autor: Qjanusz | data: 6/06/20 | godz.: 00:10)

w cache inclusive aktualizacja niższej warstwy odbywa się zawsze automatycznie, bez udziału RAM.

Teraz żebym dobrze zrozumiał, w przypadku exclusive oznacza to że np L3 pobiera dane z L2 poprzez RAM? To by było kanibalizowanie czasów dostępu do cache.

- Qjanusz (autor: kombajn4 | data: 6/06/20 | godz.: 05:47)

Jeżeli tak cię to interesuje radze sprawdzić jak to robi AMD bo oni mają exlusive od niepamiętnych czasów

- @up (autor: ekspert_IT | data: 6/06/20 | godz.: 07:26)

Jak każdy wolałbym w CPU np. więcej L2 o 2MB niż L3 o 10MB. Athlon Ii X2/x4 nie miał L3 a i tak był szybszy od Pentiuma G6950 z cache L3

https://www.cpubenchmark.net/...-X2-280/1112vs2177

- ekspert_IT (autor: Markizy | data: 6/06/20 | godz.: 10:28)

tylko nie zapominaj o różnicy w zegarze wynoszącej 29% a taktowanie pamięci jest z tym zegarem powiązane. Uwzględniając ta różnice w oparciu o twój wynik to pentium jest szybszy o 16%, zakładając liniowe wzrosty.

PS też dziwiły mnie te instrukcje w intelu jak by tego nie było od dawna.

- @ kombajn (autor: Zbyszek.J | data: 6/06/20 | godz.: 12:32)

w ZEN i ZEN 2 pamięci podręczne są typu inclusive

- Zbyszek.J (autor: kombajn4 | data: 6/06/20 | godz.: 16:06)

A to nawet nie wiedziałem. Ciekawe dlaczego to zmienili.

- taaa... (autor: Star Rider | data: 6/06/20 | godz.: 17:13)

Nazwa brzmi jak nowy zestaw "podatności" w procesorach Intela...

- "podatności" (autor: pawel1207 | data: 8/06/20 | godz.: 23:30)

sa w karzdym procesorze tak czy owak :D im bardzij jest dana architektora popularna tym wiecej z czasem kwiatkow wychodzi :D a intelowy arch praktycznie stoi w miejscu od kilku lat zmiany sa w praktyce tylko kosmetyczne ..

|

|

|

|

|

|

|

|

|

D O D A J K O M E N T A R Z |

|

| |

|

Aby dodawać komentarze, należy się wpierw zarejestrować, ewentualnie jeśli posiadasz już swoje konto, należy się zalogować.

|

|

|

|

|

|

|

|

|

|