|

TwojePC.pl © 2001 - 2026

|

|

Wtorek 29 grudnia 2020 |

|

| |

|

Prawdopodobna specyfikacja układu Nvidia AD102

Autor: Wedelek | źródło: VideoCardZ | 06:32 |

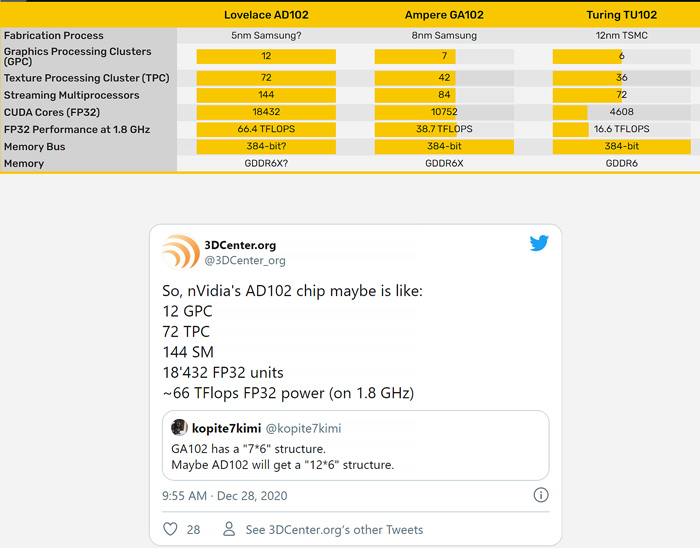

(13) |  Tydzień temu informowaliśmy Was o nowej rodzinie układów graficznych nad którymi pracuje Nvidia, podając nazwę kodową ich architektury. Zieloni zdecydowali się tym razem na wykorzystanie wizerunku znanej matematyczki - Ady Lovelace, której nazwiskiem będzie sygnowana ich nowa generacja GPU. Dziś do tych informacji dołączamy nieoficjalną specyfikację układu AD102, który będzie TOPowym przedstawicielem wspomnianej rodziny. Nowy chip ma się składać z aż 12 bloków GPC składających się z kolei z 72 klastrów TPC i 144 modułów SM. To da nam 18 432 procesory strumieniowe (144 SM x 128 SP) o łącznej wydajności na poziomie 66,4 TFLOPSa (FP 32) przy zegarze na 1,8GHz. Tydzień temu informowaliśmy Was o nowej rodzinie układów graficznych nad którymi pracuje Nvidia, podając nazwę kodową ich architektury. Zieloni zdecydowali się tym razem na wykorzystanie wizerunku znanej matematyczki - Ady Lovelace, której nazwiskiem będzie sygnowana ich nowa generacja GPU. Dziś do tych informacji dołączamy nieoficjalną specyfikację układu AD102, który będzie TOPowym przedstawicielem wspomnianej rodziny. Nowy chip ma się składać z aż 12 bloków GPC składających się z kolei z 72 klastrów TPC i 144 modułów SM. To da nam 18 432 procesory strumieniowe (144 SM x 128 SP) o łącznej wydajności na poziomie 66,4 TFLOPSa (FP 32) przy zegarze na 1,8GHz.

Plotki sugerują, że opisywany GPU będzie wytwarzany w nowej litografii 5nm od Samsunga i że Nvidia zachowa 384-bitową szynę danych. Za tymi rewelacjami stoi użytkownik Tweetera o pseudonimie @kopite7kimi - autor wielu sprawdzonych przecieków.

Czy i tym razem ma on rację przekonamy się pewnie dopiero za kilka lub nawet kilkanaście miesięcy. Zakładając, że tak, to czeka nas kolejny duży skok wydajności, ale tym razem okupiony wzrostem ceny i samego układu, który będzie mieć niemal 2x więcej jednostek niż GA102.

|

| |

|

|

|

|

|

|

|

|

|

|

K O M E N T A R Z E |

|

| |

|

- no i fajno (autor: Mario2k | data: 29/12/20 | godz.: 11:26)

Taka specyfikacja gwarantuje średni wzrost wydajności w na poziomie 55-60% w stosunku do odpowiedników z rodziny Ampere.

- prawie dwa razy więcej jednostek (autor: GULIwer | data: 29/12/20 | godz.: 11:49)

nawet jeśli 5nm da 30% mniej zużycia energii to niezły potworek będzie.

- @2. (autor: Mariosti | data: 29/12/20 | godz.: 13:36)

1.6*0.7 daje mniej więcej 1.1, czyli podobnie prądożerne a nawet minimalnie bardziej mogą być od obecnych.

- ummmm (autor: Mario2k | data: 29/12/20 | godz.: 13:59)

No to bez AiO można będzie zapomnieć o RTX 4080

- hmm (autor: GULIwer | data: 29/12/20 | godz.: 14:01)

12/7 * 0,7 = 1,2. 20% od 350W to już 420W będzie. Nową wtyczkę znowu wymyślą czy dodadzą 6-pin ;)

- @1. (autor: Saturn64 | data: 29/12/20 | godz.: 14:09)

Trudno powiedzieć, czy tak dobrze będzie się skalować przy 384bit szynie danych. Szybkość pamięci raczej nie wzrośnie w tym czasie.

- jak wy liczycie to (autor: beiks | data: 29/12/20 | godz.: 19:59)

1.6*0.7 czy 12/7 * 0,7 ?

- ano (autor: GULIwer | data: 29/12/20 | godz.: 22:53)

Ampere ma 7 clusterów a Lovelace ma mieć 12. Zakładamy podobną ilość tranzystorów w każdym, więc będzie 12/7 ~1,7 elementów które będą potrzebowały energii w stosunku Lovelace do Ampere. Zakładamy też że przejście z 8 na 5nm da 30% zmniejszenie zapotrzebowania na energię (wersja mocno optymistyczna) stąd 100-30 = 70% > 0,7. 12/7 * 7/10 fajnie się skraca jak się robi obliczenia na ułamkach zwykłych do 12/10 a zapotrzebowanie na energię 3090 znamy.

Takie liczenie na chłopski rozum. Trzeba wziąć pod uwagę też to że nV może zwiększyć ilość jednostek RT bo wydajność wciąż kuleje (nawet Hardware Unboxed postraszyli tym, że nie dostaną więcej kart "za darmo" od nich do testów, jak nie zmienią podejścia do testów RT i nie zwiększą nacisku na to). Czyli jest ciśnienie na RT w nV bo AMD dogoniło a nawet czasem przegoniło juz nV w wydajności bez-RT.

- errata (autor: GULIwer | data: 29/12/20 | godz.: 23:01)

coś mnie tknęła i sprawdziłem te % z przejścia 8 na 5 i wygląda na to że to będzie 20% ale z 7 na 5 tylko czy Samsung ma proces 7nm? https://news.samsung.com/...tra-low-power-benefits

To 30% to mi się z info o TSMC wzięło. https://www.iclarified.com/...nm-and-3nm-processes

- jakby co (autor: GULIwer | data: 29/12/20 | godz.: 23:16)

to 12/7 * 8/10 * 350W mi wyszło 480W O_O a powiedzmy podwoją ilość RT cores to niech będzie extra 50W i chyba 2x12pin będzie bo wychodzi 3x8pin (3x150W + 75 z gniazda PCIe) a to już ciężko by było upchać

- ustawiam się w kolejce (autor: MatiZ | data: 30/12/20 | godz.: 08:23)

na xkomie

- @10. (autor: Mariosti | data: 30/12/20 | godz.: 10:45)

RT Cores nie są osobnym bytem, za to całą reszta gpu wygląda na to że nie urośnie jeśli ma mieć tą samą szerokość kontroler ram, a kontroler plus sam ram na płytce to dość znacząca część całego TDP karty także bardziej realistyczne jest liczenie jednak ekwiwalentu 60% zwiększenia zapotrzebowania na energię przy wykonaniu w obecnym procesie i potem uwzględnienie 30% spadku zapotrzebowania na energię nowego procesu.

Wciąż to daje zmianę z 350W na 385W, czyli dalej absurdalnie wręcz dużo.

- @12 (autor: GULIwer | data: 30/12/20 | godz.: 11:49)

Wiem że RT cores nie są oddzielnym bytem ale nV może ześcieć upakować w każdy cluster ich więcej korzystając że nowszy proces umożliwia większą gęstość tranzystorów. Nich to da 4W na cluster x12 mamy 48W.

Co do RAMu to raczej nie aż 40% bo jak czy Der8auer czy Gamer NExus analizują PCB to proporcje power stages GPU/RAM są mniej więcej 6-7/1

Jak już sprawdziłem samsung pisze żę tylko 20% mniej energii przy tym samym poziomie wydajności a przecież może sobie zarzyczyć większego ;)

|

|

|

|

|

|

|

|

|

D O D A J K O M E N T A R Z |

|

| |

|

Aby dodawać komentarze, należy się wpierw zarejestrować, ewentualnie jeśli posiadasz już swoje konto, należy się zalogować.

|

|

|

|

|

|

|

|

|

|