|

TwojePC.pl © 2001 - 2026

|

|

Środa 24 lutego 2021 |

|

| |

|

Rynkowa premiera Rocket Lake-S odbędzie się 15 marca

Autor: Wedelek | źródło: VideoCardZ | 18:11 |

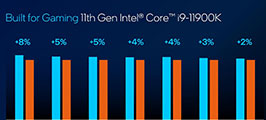

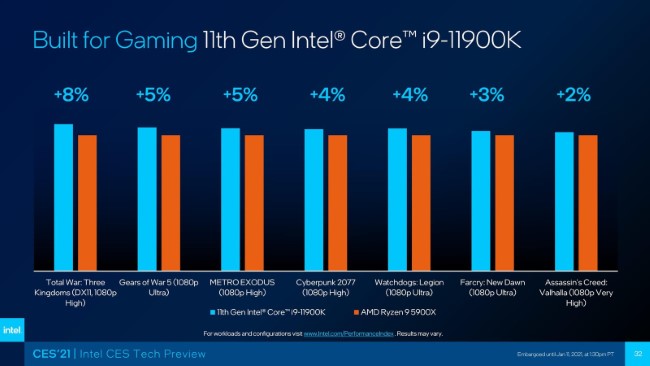

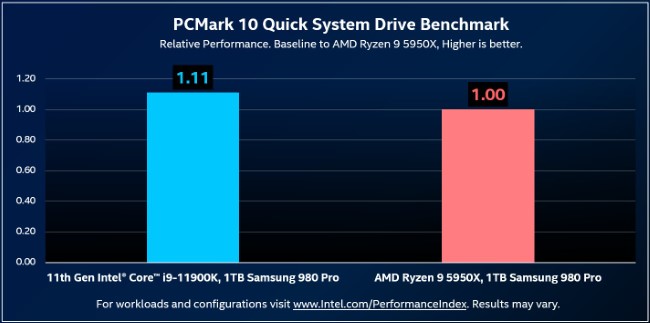

(5) |  Wygląda na to, że Intel zdecydował się nieznacznie przyspieszyć premierę swoich desktopowych procesorów z rodziny Rocket Lake-S, wyznaczając ich nową datę premiery na 15 marca bieżącego roku. Mniej więcej dwa tygodnie później procesory te mają trafić do sprzedaży, a w sieci pojawią się pierwsze obiektywne testy nowych chipów. Data zniesienia embargo na publikacje to teraz 30 marca. Sam Intel przekonuje, że jego najnowsze CPU będą około 3-8% wydajniejsze w grach niż układy czerwonych, a zaszyty w nim kontroler PCI-Express 4.0 pozwala osiągnąć dyskom SSD o 11% wyższe transfery danych niż po podpięciu do konkurencyjnych Ryzenów. Wygląda na to, że Intel zdecydował się nieznacznie przyspieszyć premierę swoich desktopowych procesorów z rodziny Rocket Lake-S, wyznaczając ich nową datę premiery na 15 marca bieżącego roku. Mniej więcej dwa tygodnie później procesory te mają trafić do sprzedaży, a w sieci pojawią się pierwsze obiektywne testy nowych chipów. Data zniesienia embargo na publikacje to teraz 30 marca. Sam Intel przekonuje, że jego najnowsze CPU będą około 3-8% wydajniejsze w grach niż układy czerwonych, a zaszyty w nim kontroler PCI-Express 4.0 pozwala osiągnąć dyskom SSD o 11% wyższe transfery danych niż po podpięciu do konkurencyjnych Ryzenów.

Rocket Lake-S ma być też mocniejszy od układów AMD, a przynajmniej jeśli chodzi o pojedynczy wątek, bo w testach wielordzeniowych nadal będą odstawać od swoich konkurentów.

Przypominam, że procesory Rocket Lake-S będą bazować na maksymalnie 8-miu rdzeniach Cypress Cove oraz układach IGP Gen12, a ich produkcja będzie realizowana w litografii 14nm+++.

|

| |

|

|

|

|

|

|

|

|

|

|

K O M E N T A R Z E |

|

| |

|

- Do h pana (autor: DrLamok | data: 25/02/21 | godz.: 19:11)

Od dawna wiadomo że nie czytasz tego co piszesz/wklejasz/tłumaczysz translatorem. Ale kurna chata nawet tematu nie przeczytać przed publikacją newsa? Really??

"Rynkowa premiera Rocekt Lake-S odbędzie się 15 marca"

- @temat (autor: Dzban | data: 25/02/21 | godz.: 22:20)

Premiera 15 marca a zniesienie embarga 30 marca? To nie ma sensu.

- @temat. (autor: Mariosti | data: 26/02/21 | godz.: 11:53)

I to jest konkurencja, intel walczy.

Owszem, wykresy mocno wybiórcze, różnica w grach minimalna i z premedytacją nie ma na wykresach ryzena 5800x który miałby prawie te same wyniki co 5950X, ale to jest biznes power pointowy. Wszyscy to robią.

- CypressCove (autor: PCCPU | data: 1/03/21 | godz.: 02:39)

Overall, looking at the changes in the CypressCove microarchitecture compared to Skylake, the average IPC increase of 18% should be on the bank because Intel did not introduce such large changes between the previous microarchitecture, which is quite intriguing.

Sunny / CypressCove

5-Way Instruction Assignment (Skylake 4-Way, Haswell 4-Way, SandyBridge 4-Way, Nehalem 4-Way, Conroe (Core 2) 4-Way)

Instruction re-queuing (OoO (ROB)) 352 entries in flight (Skylake 224, Haswell 192, SandyBridge 168, Nehalem 128, Conroe (Core 2) 96)

Scheduler 160 entries (Skylake 97, Broadwell 64, Haswell 60, SandyBridge 54, Nehalem 36, Conroe (Core 2) 32)

Register Files - Integer 280 entries + FP 224 entries (Skylake 180 + 168, Haswell 168 + 168, SandyBridge 160 + 144, Nehalem N / A, Conroe (Core 2) N / A)

Dispatch 10-Way (dispatch from scheduler (execution unit ports)) (Skylake 8-Way, Haswell 8-Way, SandyBridge 6-Way, Nehalem 6-Way, Conroe (Core 2) 6-Way)

- UpEDIT (autor: PCCPU | data: 1/03/21 | godz.: 02:40)

Ogólnie patrząc na zmiany w mikroarchitekturze CypressCove względem Skylake to średni wzrost IPC 18% powinien być na bank ponieważ tak dużych zmian Intel nie wprowadzał między poprzednimi mikroarchitekturami co jest dość intrygujące.

Sunny/CypressCove

Przydział instrukcji 5-Way (Skylake 4-Way, Haswell 4-Way, SandyBridge 4-Way, Nehalem 4-Way, Conroe(Core 2) 4-Way)

Przekolejkowywanie instrukcji(OoO(ROB)) 352 wpisy w locie (Skylake 224, Haswell 192, SandyBridge 168, Nehalem 128, Conroe(Core 2) 96)

Scheduler 160 wpisów (Skylake 97, Broadwell 64, Haswell 60, SandyBridge 54, Nehalem 36, Conroe(Core 2) 32)

Register Files - Integer 280 wpisów + FP 224 wpisów (Skylake 180+168, Haswell 168+168, SandyBridge 160+144, Nehalem N/A, Conroe(Core 2) N/A)

Dispatch 10-Way(wysyłka z schedulera(porty jednostek wykonawczych)) (Skylake 8-Way, Haswell 8-Way, SandyBridge 6-Way, Nehalem 6-Way, Conroe(Core 2) 6-Way)

|

|

|

|

|

|

|

|

|

D O D A J K O M E N T A R Z |

|

| |

|

Aby dodawać komentarze, należy się wpierw zarejestrować, ewentualnie jeśli posiadasz już swoje konto, należy się zalogować.

|

|

|

|

|

|

|

|

|

|