|

TwojePC.pl © 2001 - 2026

|

|

Poniedziałek 15 marca 2021 |

|

| |

|

Zdjęcie rdzenia procesorów Intel Rocket Lake-S

Autor: Zbyszek | źródło: WccFTech | 10:46 |

(8) |  Obecna 10 generacja procesorów Core od Intela, czyli procesory o nazwie kodowej Comet-Lake S ze swoim liderem Core i9-10900K na czele, debiutowały w maju 2020 roku. W poczekalni czekają jednak już ich następcy w postaci procesorów Rocket Lake-S, czyli Core 11. generacji, których oficjalny debiut odbędzie się jeszcze dzisiaj. Nowe CPU otrzymały rdzenie Cypress Cove z kilkanaście % wyższym wskaźnikiem IPC, oraz ulepszony IGP oparty o architekturę XE i zapewniający o około 50% lepszą wydajność. Niestety Rocket Lake-S są nadal wytwarzane w 14nm litografii, co ma pewne konsekwencje. Obecna 10 generacja procesorów Core od Intela, czyli procesory o nazwie kodowej Comet-Lake S ze swoim liderem Core i9-10900K na czele, debiutowały w maju 2020 roku. W poczekalni czekają jednak już ich następcy w postaci procesorów Rocket Lake-S, czyli Core 11. generacji, których oficjalny debiut odbędzie się jeszcze dzisiaj. Nowe CPU otrzymały rdzenie Cypress Cove z kilkanaście % wyższym wskaźnikiem IPC, oraz ulepszony IGP oparty o architekturę XE i zapewniający o około 50% lepszą wydajność. Niestety Rocket Lake-S są nadal wytwarzane w 14nm litografii, co ma pewne konsekwencje.

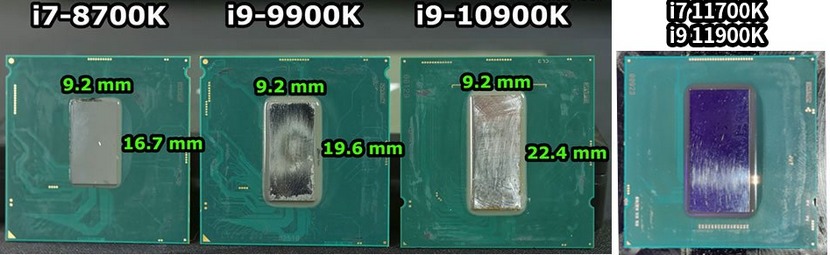

Poza poborem energii i liczbą wydzielanego ciepła, jedną z nich jest rozmiar rdzenia krzemowego nowych procesorów.

W sieci właśnie pojawiło się zdjęcie Core i9-11900K ze zdjętą osłoną termiczną. Rdzeń krzemowy Rocket Lake-S ma podobną długość do rdzenia Comet-Lake S, ale jest zauważalnie szerszy. Zmierzona powierzchnia to około 270 mm2, podczas gdy rdzeń dotychczasowych procesorów Comet-Lake-S zajmował 206 mm2, i to pomimo obecności dwóch rdzeni więcej.

|

| |

|

|

|

|

|

|

|

|

|

|

K O M E N T A R Z E |

|

| |

|

- czego oni tam dołożyli (autor: GULIwer | data: 15/03/21 | godz.: 16:18)

ze powierzchnia urosła o 30% przy wycięciu 20% rdzeni? Czyżby łatki na dziury?

- @up (autor: Saturn64 | data: 15/03/21 | godz.: 17:42)

Podobno, że AVX512. No może jeszcze jakieś specjalne ulepszenia dla machiny Zuckerberga, by mógł lepiej trafiać do nas z reklamami.

- @Up (autor: PCCPU | data: 16/03/21 | godz.: 00:07)

Rdzeń CypressCove złożony jest z 300 milionów tranzystorów a rdzeń Skylake to 217 milionów tranzystorów.

Pojedynczy rdzeń x86 CypressCove zajmuje około 38% większą powierzchnię niż Skylake.

Inaczej - 8 rdzeni CypressCove zajmuje o 11% większą powierzchnię niż 10 rdzeni Skylake a do tego trzeba jeszcze dodać kontrolery i IGP.

Nie sądzę by AVX512F stanowił największą zmianę bo chociażby m.in scheduler ma 160 wpisów zamiast 97 wpisów w Skylake.

A tu wykaz najważniejszych choć nie wszystkich zmian w CypressCove:

Rdzeń x86 Skylake 217 milionów tranzystorów

Front-end

Cache L1-Instrukcji 32KB 8-Way

µOP cache 1536 wpisów

ITLB 8 wpisów(2M)

Allocation Queue(IDQ) 64 µOP/wątek lub 128 µOP pojedynczy wątek

LSD może wykryć do 64 µOP pętli/wątek lub 128 µOP pojedynczy wątek

5-cio drożny dekoder x86(1 kompleksowy, 4 proste)

Back-end

Przydział instrukcji 4-Way

Przekolejkowywanie instrukcji(OoO(ROB)) 224 wpisy w locie

Scheduler 97 wpisów

Register Files - Integer 180 wpisów + FP 168 wpisów

Dispatch 8-Way(wysyłka z schedulera(porty jednostek wykonawczych))

Execution Engine

3x FP-ALU(Jednostki arytmetyczno-logiczne-zmienno-przecinkowe(2x FMAC 256bit))

1x ALU(Jednostka arytmetyczno-logiczna)

1x StoreData(magazyn danych)

3x AGU(2x ładowanie adresów, 1x generowanie adresów)

Memory subsystem

In-Flight Loads 72 wpisy (ładowanie w locie z L1D)

In-Flight Stores 56 wpisów (magazynowanie w locie do L1D)

Cache L1-Danych 32KB 8-Way

Cache L2 256KB 4-Way

------------------------------------------------------------------------------------------------------------------------

Rdzeń x86 CypressCove 300 milionów tranzystorów

Front-end

Cache L1-Instrukcji 32KB 8-Way

µOP cache 2250 wpisów

Smarter prefetchers(inteligentniejszy preselektor)

Improved Branch Predictor(ulepszony predyktor gałęzi)

ITLB 16 wpisów(podwójne 2M)

Allocation Queue(IDQ) 70 µOP/wątek lub 140 µOP pojedynczy wątek

LSD może wykryć do 70 µOP pętli/wątek lub 140 µOP pojedynczy wątek

5-cio drożny dekoder x86(1 kompleksowy, 4 proste)

Back-end

Przydział instrukcji 5-Way

Przekolejkowywanie instrukcji(OoO(ROB)) 352 wpisy w locie

Scheduler 160 wpisów

Register Files - Integer 280 wpisów + FP 224 wpisy

Dispatch 10-Way (wysyłka z schedulera(porty jednostek wykonawczych))

Execution Engine

3x FP-ALU(Jednostki arytmetyczno-logiczne-zmiennoprzecinkowe(1x FMAC512bit lub 2x FMAC256bit))(w rzeczywistości jest 1x FMAC512bit + 1x FMAC256bit)

1x ALU(Jednostka arytmetyczno-logiczna)

2x StoreData(magazyn danych)

2x AGU(ładowanie adresów)

2x AGU(generowanie adresów)

Memory subsystem

In-Flight Loads 128 wpisów (ładowanie w locie z L1D)

In-Flight Stores 72 wpisy (magazynowanie w locie do L1D)

Cache L1-Danych 48KB 12-Way

Cache L2 512KB 8-Way

- @up (autor: Saturn64 | data: 16/03/21 | godz.: 07:18)

Dzięki za info. Czy mógłbyś porównać zen 2 do zen 3. Wzrost IPC zen3/zen2 porównywalny z tym pomiędzy CypressCove a skylake. Jak tu prezentuje się wzrost powierzchni rdzenia? W obu przypadkach stosowane są te same węzły procesowe 7/7nm i 14/14nm.

- Saturn64 (autor: PCCPU | data: 16/03/21 | godz.: 10:28)

Z tego co kojażę to rdzeń x86 Zen3 ma kilkanaście % więcej tranzystorów. pojemność L1D, L2 i L3(stosunek na rdzeń) pozostała taka sama. Zen3 to całkowicie nowy rdzeń ponieważ cała logika sterująca i algorytmy zostały zastąpione nową agresywnie zoptymalizowaną co dało IPC wyższe od 1% do 46% z średnią 19%. Zresztą inżynierowie AMD potwierdzili że Zen3 to całkowicie nowy x86. Co do porównania Zen3 z Zen2 jak będę miał więcej czasu to umieszczę a puki co dodam tylko Zen3:

Rdzeń x86 Zen3

Front-end

Cache L1-Instrukcji 32KB 8-Way

µOP cache 4096 wpisów

4-ro drożny dekoder x86(4 kompleksowe)

Back-end

Przekolejkowywanie instrukcji(OoO(ROB)) 256 wpisy w locie

Scheduler Integer 96 wpisów

Scheduler FP 64 wpisy

Register Files Integer 192 wpisy

Register Files FP 160 wpisów

Dispatch Integer 10-Way(wysyłka z schedulera(porty jednostek wykonawczych))

Dispatch FP 3-Way(wysyłka)

Execution Engine

6x FPU(jednostki zmiennoprzecinkowe 2x FMAC256bit)

4x ALU(Jednostki arytmetyczno-logiczne)

2x StoreData(magazyn danych)

1x Dedicated Branch

3x AGU(3x ładowanie adresów lub 2x magazynowanie adresów)

Memory subsystem

In-Flight Loads 72 wpisów (ładowanie w locie z L1D)

In-Flight Stores 64 wpisy (magazynowanie w locie do L1D)

Cache L1-Danych 32KB 8-Way

Cache L2 512KB 8-Way

- @up (autor: Saturn64 | data: 16/03/21 | godz.: 11:08)

Chodziło mi o porównanie na ile procentowo zwiększył się rdzeń Zen 3 vs Zen 2. Jest to o tyle ważne, że da nam pogląd jak skutecznie lub nie skutecznie zmiana architektury spodowała owe zwiększenie rozmiaru rdzenia przy podobnych zwiększenieach IPC . Dlatego wydaje mi się w dużej mierze, że wzrost wielkości intela jest związany w dużej mierze właśnie przez AVX 512.

- @ Saturn (autor: Zbyszek.J | data: 17/03/21 | godz.: 10:26)

tu odpowiedź, ZEN3 ma 14% większą powierzchnie niż ZEN2: https://i.redd.it/o59e4sz43vy51.png

A cały chiplet urósł z 74mm2 do 80,7mm2

- @5. (autor: pwil2 | data: 20/03/21 | godz.: 21:10)

Wygląda na to, że sukcesem AMD jest zebranie zespołu ludzi, którzy potrafią projektować procesory/architektury. Jim Keller był dla nich kimś jak Gordon Ramsay, wybrał garstkę ludzi z potencjałem, przekazał wiedzę i zrobił z nich sprawnie działający zespół fachowców. Można było mieć obawy, że odwali najcięższą robotę i dalej będą już tylko siłą rozpędu rozwijać ZEN.

Szkoda, że u Intela napotkał na problemy nie do przeskoczenia.

|

|

|

|

|

|

|

|

|

D O D A J K O M E N T A R Z |

|

| |

|

Aby dodawać komentarze, należy się wpierw zarejestrować, ewentualnie jeśli posiadasz już swoje konto, należy się zalogować.

|

|

|

|

|

|

|

|

|

|