|

TwojePC.pl © 2001 - 2026

|

|

Środa 14 kwietnia 2021 |

|

| |

|

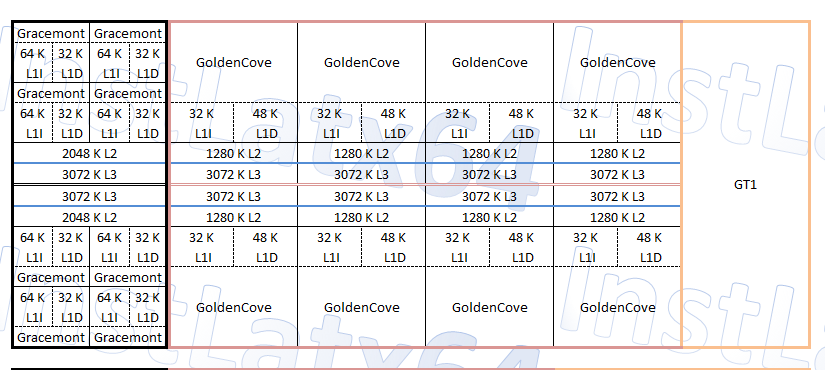

Schemat blokowy procesorów Intel Alder Lake-S

Autor: Zbyszek | źródło: WccFTech | 18:03 |

(8) |  Wszystko wskazuje na to, że w tym roku Intel wprowadzi na rynek dwie generacje procesorów. Poza debiutującymi niedawno Core 11. generacji (Rocket Lake-S, 14nm) pod koniec tego roku mają pojawić się też CPU nazywane jako Alder Lake-S, które trafią do sprzedaży albo jako Intel Core 12. generacji, albo pod zupełnie nową nazwą Intel Evo. Procesory zaoferują 8 wydajnych rdzeni z architekturą GoldenCove, które będą wsparte przez 8 energooszczędnych rdzeni w postaci Gracemont, czyli ulepszonej wersji rdzeni x86 Tremont. Alder Lake-S będą też zgodne z pamięciami DDR5 i całkowicie nową podstawką LGA 1700. Wszystko wskazuje na to, że w tym roku Intel wprowadzi na rynek dwie generacje procesorów. Poza debiutującymi niedawno Core 11. generacji (Rocket Lake-S, 14nm) pod koniec tego roku mają pojawić się też CPU nazywane jako Alder Lake-S, które trafią do sprzedaży albo jako Intel Core 12. generacji, albo pod zupełnie nową nazwą Intel Evo. Procesory zaoferują 8 wydajnych rdzeni z architekturą GoldenCove, które będą wsparte przez 8 energooszczędnych rdzeni w postaci Gracemont, czyli ulepszonej wersji rdzeni x86 Tremont. Alder Lake-S będą też zgodne z pamięciami DDR5 i całkowicie nową podstawką LGA 1700.

W sieci właśnie pojawił się schemat przedstawiający wewnętrzną budowę tych CPU. Poszczególne rdzenie w Alder Lake-S będą rozmieszczone w sposób przypominający ten, jaki Intel stosuje już od kilku lat. Rdzenie zostaną ułożone w dwóch rzędach, a pomiędzy nimi znajdzie się łącząca je pamięć podręczna 3 poziomu z magistralą typu Ring Bus.

Z kolei energooszczędne rdzenie Gracemont zostaną umieszczone w układzie w podobny sposób - w dwóch grupach po 4 rdzenie zajmą miejsce, które w przypadku ich braku przypadłoby na 9 i 10 rdzeń GoldenCove.

Informacje wskazują też na budowę podsystemu pamięci podręcznych w procesorach Alder Lake-S. Na każdy rdzeń GoldenCove przypadać będzie 3MB pamięci L3 i 1,25MB pamięci L2. Z koleii grupy 4 rdzeni Gracemont otrzymają po 3MB pamięci L3 i 2MB pamięci L2. Zaskakuje pojemność pamięci L1 dla instrukcji - mocniejsze rdzenie GoldenCove posiadają jej 32 KB, podczas gdy słabsze rdzenie Gracemont mają jej 2 razy więcej - 64 KB. Pamięć L1 dla danych to 48 KB w rdzeniach GoldenCove i 32 KB w rdzeniach Gracemont.

|

| |

|

|

|

|

|

|

|

|

|

|

K O M E N T A R Z E |

|

| |

|

- Czyli potwierdzona (autor: PCCPU | data: 14/04/21 | godz.: 23:34)

konfiguracja i ilość cache GoldenCove która jest bardzo podobna(przynajmniej w kwestii pojemnośi) do tej w WillowCove).

- Edit (autor: PCCPU | data: 15/04/21 | godz.: 01:24)

Ktoś zrobił tabelkę na podstawie dostępnych danych lub spekulacji.

- ... (autor: pwil2 | data: 15/04/21 | godz.: 04:13)

Pamięć L3 najpewniej będzie wspólna dla wszystkich rdzeni - łącznie 30MB. L2 to 1.25MB dla każdego z szybszych i 512KB dla każdego z wolniejszych rdzeni.

- c.d. (autor: pwil2 | data: 15/04/21 | godz.: 04:14)

L1 jest tak dobrane, by wykorzystać przestrzeń i 4x Atomowy rdzeń zajmował tyle miejsca co jeden mocniejszy.

- c.d. (autor: pwil2 | data: 15/04/21 | godz.: 04:15)

Mogli pomieścić 10 rdzeni wydajniejszych, ale źle by to w materiałach marketingowych wyglądało, a tak będzie "16-core procesor".

- Znalazłem coś takiego (autor: PCCPU | data: 16/04/21 | godz.: 01:37)

"The nm sizes are marketing - esp when dealing with TSMC. TSMC sells it's processes - so every little tiny thing turns into a new product there.

TSMC's 7nm is roughly equiv to Intel's 10nm (Ice Lake) process, Intel's 10nm SF (Tiger Lake) process is as dense as TSMC's 7nm+.

TSMC's 6nm is just an optimized 7nm, and 5nm is not even a half node more dense... TSMC's claims about density are best case test patterns - same as Intel and Samsung.

Intel's 14nm has gone through so many advances, that it's hardly 14nm anymore - anyone who thinks that Gen 1 14nm is anything like last Gen (Rocket Lake) 14nm is clueless. IF TSMC had been in charge of naming that process -it would be called 8nm... Intel doesn't sell it's capacity to other companies - once they start their contract foundry work - the naming will be much closer to TSMC.

Intel's Full EUV 7nm is roughly equiv to between N5 and N3 - so an "N4" - which is a much more sophisticated process than TSMC's. Intel delays in its 7nm process is because they are fabricating ALL layers with EUV and not just a couple - and their move to Cobalt is also unmatched by TSMC - and IF TSMC's pie in the sky 3nm was any denser than Intel's 7nm the move to Cobalt over Copper would be required - simple physics... at macro scale copper is a superior conductor vs cobalt - at nano scales copper becomes a resistor and cobalt becomes a much better conductor - most of the advances in 10nm SuperFin ae due to cobalt.

Intel's Full EUV 7nm+ (1st gen is Xe HPC with the compute tiles in the already being tested chip is Intel's Full EUV 7nm process - Xe HPC was always going to be the launch product for that process) will be closer to N3 than N4. Progress is slower when you are doing the hard things.

"Intel reports a density of 100.76MTr/mm2 (mega-transistor per squared millimetre) for its 10nm process, while TSMC's 7nm process is said to land a little behind at 91.2MTr/mm2 (via Wikichip). Not that it'll do you much good on desktop—Intel's yet to produce 10nm desktop processors. AMD Ryzen on the other hand…." from PC Gamer.

Intel's 10nm SF and ESF would be more dense than "vanilla" 10nm - and TSMC's 7nm+ would be denser than their "vanilla" 7nm.

electronicsweek...

There will be a move away from the "nm" to density (transistors per square millimeter)."

Google translator:

"Rozmiary nm mają charakter marketingowy - szczególnie w przypadku TSMC. TSMC sprzedaje swoje procesy - więc każda mała rzecz zamienia się tam w nowy produkt.

7nm TSMC jest z grubsza równoważne procesowi 10nm Intela (Ice Lake), proces 10nm SF (Tiger Lake) Intela jest tak gęsty, jak proces 7nm + TSMC.

6 nm TSMC to po prostu zoptymalizowane 7 nm, a 5 nm nie jest nawet o pół węzła bardziej gęste ... Twierdzenia TSMC o gęstości są najlepszymi wzorcami testowymi - tak samo jak Intel i Samsung.

Technologia 14nm Intela przeszła tak wiele postępów, że prawie nie jest już 14nm - każdy, kto myśli, że 14nm 1.generacji jest czymś podobnym do 14nm ostatniej generacji (Rocket Lake), nie ma pojęcia. IF TSMC było odpowiedzialne za nazwanie tego procesu - będzie się nazywał 8nm ... Intel nie sprzedaje swojej mocy innym firmom - po rozpoczęciu odlewni kontraktowej - nazewnictwo będzie znacznie bliższe TSMC.

Pełne EUV 7nm Intela jest z grubsza równoważne między N5 i N3 - a więc „N4” - co jest procesem znacznie bardziej wyrafinowanym niż TSMC. Opóźnienia Intela w procesie 7 nm wynikają z tego, że produkują WSZYSTKIE warstwy za pomocą EUV, a nie tylko kilku - a ich przejście na Cobalt jest również niezrównane przez TSMC - a ciasto IF TSMC na niebie 3 nm było gęstsze niż 7 nm Intela w przypadku przejścia na kobalt ponad Miedź byłaby wymagana - prosta fizyka ... w skali makro miedź jest lepszym przewodnikiem niż kobalt - w nanoskali miedź staje się rezystorem, a kobalt staje się znacznie lepszym przewodnikiem - większość postępów w 10nm SuperFin ae jest spowodowana kobaltem.

Pełne EUV 7nm + Intela (pierwsza generacja to Xe HPC z kafelkami obliczeniowymi w już testowanym układzie to proces Intel Full EUV 7nm - Xe HPC zawsze miał być produktem wprowadzającym dla tego procesu) będzie bliżej N3 niż N4. Postęp jest wolniejszy, gdy robisz trudne rzeczy.

„Intel podaje gęstość 100,76 MT / mm2 (mega-tranzystor na milimetr kwadratowy) w procesie 10 nm, podczas gdy proces TSMC 7 nm ma być nieco mniejszy przy 91,2 mln Tr / mm2 (przez Wikichip). jesteś dobry na komputerach stacjonarnych - Intel jeszcze nie wyprodukował 10-nanometrowych procesorów do komputerów stacjonarnych. Z drugiej strony AMD Ryzen… ”. z PC Gamer.

10nm SF i ESF Intela byłyby bardziej gęste niż „waniliowe” 10nm - a 7nm + TSMC byłoby gęstsze niż ich „waniliowe” 7nm.

https: //electronicsweek ...

Nastąpi odejście od "nm" do gęstości (tranzystory na milimetr kwadratowy)."

- @temat. (autor: Mariosti | data: 16/04/21 | godz.: 13:24)

Ciekawe, ale chyba jednak trochę tendencyjne w stronę wybielania intela.

Gdyby 14nm +++++ było takie dobre jak teoretyczne 8nm TSMC to przecież nie byłoby tak dramatycznej różnicy w zużyciu energii przez nowe rdzenie intela w 14nm++++++ w porównaniu do AMD w 7nm tsmc.

Poprzednim razem gdy mieliśmy odwrotną sytuację z AMD FX, intel miał i lepszą architekturę i lepszy proces i dopiero wtedy była podobna różnica w zużyciu energii przez rdzenie jak obecnie.

W czasach Pentium 4 intel miał lepszy proces i gorszą architekturę, co nadganiał nawet 50% wyższym taktowaniem niż u AMD i wtedy też mieliśmy podobną sytuację, chociaż nie było aż tak ogromnej różnicy.

- Mariosti (autor: PCCPU | data: 16/04/21 | godz.: 18:52)

https://www.reddit.com/...w_far_intel_could_really

|

|

|

|

|

|

|

|

|

D O D A J K O M E N T A R Z |

|

| |

|

Aby dodawać komentarze, należy się wpierw zarejestrować, ewentualnie jeśli posiadasz już swoje konto, należy się zalogować.

|

|

|

|

|

|

|

|

|

|