|

TwojePC.pl © 2001 - 2026

|

|

Środa 14 czerwca 2023 |

|

| |

|

TSMC opracuje Backside Power Delivery dla litografii 2nm

Autor: Zbyszek | źródło: AnandTech | 22:15 |

|  W 2021 roku Intel pochwalił się opracowaniem nowej technologii dla przyszłych procesów litograficznych - mowa o technice zasilania tranzystorów o nazwie Backside Power Delivery. Technologia jest obecnie w fazie testów, i zostanie użyta produkcyjne w przyszłym roku w kolejnej generacji efektywnych rdzeni, które będą wytwarzane w litografii Intel 20A. Technika Backside Power Delivery polega na oddzieleni linii sygnałowych od zasilających, i przeniesieniu linii zasilających na warstwy umieszczone pod tranzystorami, a więcej o jej szczegółach technicznych pisaliśmy tutaj.Takie rozwiązanie nie mogło zostać bez odpowiedzi ze strony firmy TSMC, która ogłosiła, że opracuje własną wersję rozwiązania Backside Power Delivery. W 2021 roku Intel pochwalił się opracowaniem nowej technologii dla przyszłych procesów litograficznych - mowa o technice zasilania tranzystorów o nazwie Backside Power Delivery. Technologia jest obecnie w fazie testów, i zostanie użyta produkcyjne w przyszłym roku w kolejnej generacji efektywnych rdzeni, które będą wytwarzane w litografii Intel 20A. Technika Backside Power Delivery polega na oddzieleni linii sygnałowych od zasilających, i przeniesieniu linii zasilających na warstwy umieszczone pod tranzystorami, a więcej o jej szczegółach technicznych pisaliśmy tutaj.Takie rozwiązanie nie mogło zostać bez odpowiedzi ze strony firmy TSMC, która ogłosiła, że opracuje własną wersję rozwiązania Backside Power Delivery.

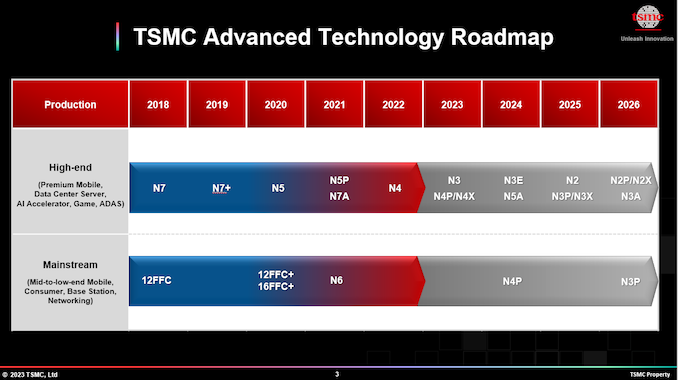

Technologia w nomenklaturze TSMC otrzymała nazwę BPDN (backside power delivery networks), i ma uzyskać status gotowości do produkcji w 2026 roku. Do stosowania BPDN przystosowany zostanie proces litograficzny N2P, czyli druga generacja 2nm litografii TSMC. Podobnie jak u Intela, rozwiązanie oddzieli linie sygnałowe od zasilających - linie sygnałowe będą umieszczone w klasyczny sposób nad tranzystorami, a linie zasilające zostaną przeniesione pod tranzystory i będą do nich doklejane oddzielnie.

|

| |

|

|

|

|

|

|

|

|

|

|

D O D A J K O M E N T A R Z |

|

| |

|

Aby dodawać komentarze, należy się wpierw zarejestrować, ewentualnie jeśli posiadasz już swoje konto, należy się zalogować.

|

|

|

|

|

|

|

|

|

|