|

TwojePC.pl © 2001 - 2026

|

|

Czwartek 17 sierpnia 2023 |

|

| |

|

Architektura RDNA 4 ma składać się z jeszcze większej liczby chipletów

Autor: Zbyszek | źródło: More Law is Dead | 12:28 |

(11) |  Karty graficzne Radeon RX 7000 z architekturą RDNA 3 to pierwsze na rynku konstrukcje dla graczy, których GPU mają tzw. budowę modułowa, czyli składają się z kilku rożnych połączonych ze sobą układów scalonych. W przypadku układu Navi 31, centralny chiplet GCD z procesorami strumieniowymi jest otoczony przez 6 dodatkowych chipletów MCD zawierających pamięć Infinity Cache i kontroler pamięci GDDR6. Tymczasem kanał More Law is Dead donosi, że opracowywane obecnie przyszłe Radeony RX 8000 z architekturą RDNA 4 otrzymają jeszcze bardziej skomplikowaną budowę GPU. W ich przypadku nawet chiplet GCD nie będzie pojedynczym układem scalonym, ale zbiorem mniejszych układów scalonych. Karty graficzne Radeon RX 7000 z architekturą RDNA 3 to pierwsze na rynku konstrukcje dla graczy, których GPU mają tzw. budowę modułowa, czyli składają się z kilku rożnych połączonych ze sobą układów scalonych. W przypadku układu Navi 31, centralny chiplet GCD z procesorami strumieniowymi jest otoczony przez 6 dodatkowych chipletów MCD zawierających pamięć Infinity Cache i kontroler pamięci GDDR6. Tymczasem kanał More Law is Dead donosi, że opracowywane obecnie przyszłe Radeony RX 8000 z architekturą RDNA 4 otrzymają jeszcze bardziej skomplikowaną budowę GPU. W ich przypadku nawet chiplet GCD nie będzie pojedynczym układem scalonym, ale zbiorem mniejszych układów scalonych.

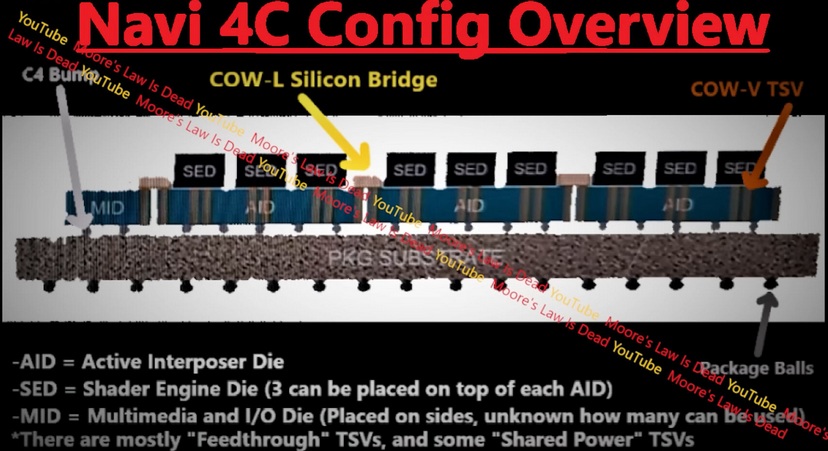

Dlatego też zamiast nazwy GCD (Graphisc Core Die), zastosowana zostanie nazwa SED (Shader Engine Die). Trzy chiplety SED mają być montowane na chiplecie AID, zawierającym pamięć Infinity Cache oraz jednocześnie będącym aktywnym interposerem (tzn. łącznikiem) dla umieszczonych wyżej chipletów SED.

Zestawy chiplet AID plus trzy chiplety SED mają być stosowane w przyszłych Radeonach RX 8000 w różnych ilościach: np. najtańsze karty otrzymają jeden chiplet AID z trzema chipletami SED, a najbardziej wydajne otrzymają przykładowo cztery chiplety AID, i łącznie 12 umieszczonych na nich chipletów SED. W każdym przypadku, niezależnie od liczby stosowanych chipletów AID+SED, stosowany będzie też jeden dodatkowy chiplet MID (Multimedia and I/O Die), zawierający kontrolery wyświetlaczy, dekodery multimediów i interfejs dla złącza PCI-Express x16.

W sieci powstała też wizualizacja, jak potencjalnie wyglądać może przyszły układ graficzny AMD z architekturą RDNA 4 - w tym przypadku wizualizowany jest GPU z trzema chipletami AID, na każdym z nich trzy chiplety SED (łącznie 9 szt) oraz dodatkowy chiplet MID.

|

| |

|

|

|

|

|

|

|

|

|

|

K O M E N T A R Z E |

|

| |

|

- przekombinowane (autor: GULIwer | data: 17/08/23 | godz.: 22:32)

ale może się uda.

- też mi się tak wydaje (autor: Zbyszek.J | data: 17/08/23 | godz.: 23:44)

koszt łącznia wszystkiego w całość za duży względem korzyści otrzymywanych na wyższym uzysku wynikających z produkowania mniejszych układów scalonych.

Zrobiliby po prostu jeden chiplet MID (kontrolery wyświetlaczy, dekodery multimediów i interfejs dla złącza PCI-Express x16), będący odpowiednikiem IOD w Ryzenach.

Do niego dokładne byłby 1, 2, 3, 4, 5 czy 6 innych zwykłych monolitycznych (bez interposera) chipletów SCD (Shader Core Die) z procesorami strumieniowymi, Infinity Cache i bezpośrednim interfejsem do GDDR6/GDDR7.

Na wzór Ryzenów:

Czyli wszystko co co musi być wypychamy do czegoś ala IOD, i do IOD przyklejamy n-sztuk SCD (Shader Core Die) komunikujące się z GDDR.

Przykładowo

IOD + 1 SCD = 1024 procesory strumieniowe i 64-bitowy (4GB) interfejs GDDR6

IOD + 2 SCD = 2048 procesory strumieniowe i 128-bitowy (8GB) interfejs GDDR6

IOD + 3 SCD = 3072 procesory strumieniowe i 192-bitowy (12GB) interfejs GDDR6

IOD + 4 SCD = 4096 procesorów strumieniowych i 256-bitowy (16GB) interfejs GDDR6

IOD + 5 SCD = 5120 procesorów strumieniowych i 320-bitowy (20GB) interfejs GDDR6

IOD + 6 SCD = 6144 procesorów strumieniowych i 384-bitowy (24GB) interfejs GDDR6

Kopia podejścia z Ryzeów / EPYCów wydaje się tu dość logicznym kierunkiem. W odróżnieniu od RDNA 3 - gdzie pozostawienie wszystkich shaderów w jednym układzie krzemowym i wydzielenie z nich Infinity Cache do oddzielnych kawałków krzemowych to raczej porażka - duży wzrost latency (opóźnień) w komunikacji z GDDR6 = spadek efektywnej przepustowości GPU (shaderów) do pamięci i efekt końcowy - przeciętna wydajność.

- @2 składaj papiery do AMD (autor: rarek | data: 17/08/23 | godz.: 23:52)

W PL są sami trenerzy piłkarscy i jak widać projektanci procesorów.

- @ rarek (autor: Zbyszek.J | data: 18/08/23 | godz.: 00:00)

ja piszę jako amator - mają świetne rozwiązania chipletowe stosowane w Ryzenach / EPYC, a w przypadku graficznych RDNA zamiast zastosować ich wariant, to próbują odkryć koło na nowo... (tzn. próbują całkowicie coś innego).

- jeszcze dodam (autor: Zbyszek.J | data: 18/08/23 | godz.: 00:10)

że GPU jest dużo bardziej od CPU wrażliwy na opóźnienia w dostępie do pamięci operacyjnej (DDR/GDDR), więc w RDNA 3 wydzielenie Infinity Cache i kontrolera GDDR6 do odrębnego chipu krzemowego to był strzał w stopę. I każdy inżynier w AMD powinien to wiedzieć już ~3-4 lata temu na starcie tego projektu.

Rarek popatrz tu: https://chipsandcheese.com/...aphics-architecture/

Pierwszy wykres - powyżej 6MB (pojemność L2 w Navi 31), opóźnienia w dostępie do pamięci w RDNA 3 są dużo wyższe niż opóźnienia w dostępnie do pamięci w RDNA 2. Infinity Cache w RDNA 3 jest wolniejsze i ma większe opóźnienia, niż Infinity Cache w RDNA 2. Właśnie dlatego, że ta pamięć w RDNA 3 jest w oddzielnym chipie krzemowym.

- Zbyszek.J (autor: Markizy | data: 18/08/23 | godz.: 08:06)

niekoniecznie musi tak być, przy navi 33 do navi 23 mamy zerowy wzrost wydajności a obydwa są monolitem, maja taka samą ilość jednostek i podobne taktowania. To co się poprawia to pobór energii. To nie o samą czas dostępu idzie a o przepustowość która dla gpu jest bardziej znacząca.

- Zbyszek.J (autor: Markizy | data: 18/08/23 | godz.: 09:03)

ja bym zrobił inny podział, SSD miałby 2024SP i 128bit.

IOD + 1 SCD 1536/2048 z 6/8GB GDDR6, ewentualnie 6GB dla słabszego wariantu i 8GB dla mocniejszego (szyna 96/128bit)

IOD + 2 SCD 3536(3072)/4096 z 12/16GB GDDR6 odpowiednio szyna 192/256

IOD + 3 SCD 5210/5632/6144 z 20/24GB gdzie mamy już 3 warianty pierwszy 5120SP 320bit 20GB GDDR6(320bit), kolejny 5632SP 24GB GDDR6 (384bit) oraz 6144SP 24GB GDDR7 (384bit).

Pod koniec następnego roku produkcja gddr7 powinna ruszyć, ponadto nie przewiduje że pierwsze karty z rdna4 zobaczymy szybciej niż w 2025r.

Twoje rozwiązanie z 6 SCD byłoby dobre gdyby nie problemy z komunikacją pomiędzy poszczególnymi układami. Lepiej żeby ogarnęli to dla mniejszej ilości układów niż dla większej. Inaczej wrócimy do historii z CF i SLI gdzie raz działało to dobrze raz słabo a jeszcze częściej w cale. Akurat układu GPU są bardziej wrażliwe na wymianę danych miedzy sobą niż CPU które może działać niezależnie.

- @ZbyszekJ (autor: Promilus | data: 18/08/23 | godz.: 20:00)

Panie, co pan nie powiesz, a jak tłumaczyli na samym początku co jest problematyczne w robieniu chipletów GPU to spał, srał czy nie rozumiał? Polecam wrócić do prezentacji Lisy gdzie jest to wytłumaczone zamiast pierdzielić 3 po 3. GPU to inna bajka! Już to, że udało im się w ogóle w jakikolwiek sposób chiplety zrobić jest nie lada osiągnięciem, a to że jeszcze chcą to rozdrobnić to już w ogóle. NV badała temat już z 5 lat temu i dała sobie na wstrzymanie do czasu aż nie będzie totalnie innej możliwości. Koszty produkcji b.dużych układów są nieproporcjonalnie większe niż kilku małych o tej samej łącznej powierzchni i przy pozycji rynkowej AMD nie może sobie pozwolić na tego typu umowy jakie podpisuje Apple (bierem każdy najnowszy proces niezależnie od uzysku) czy NV (bierem wielgie monolity ponosząc koszty ujowych).

- To co Zbyszek napisał ma ręce i nogi (autor: Qjanusz | data: 21/08/23 | godz.: 12:17)

Sam się zsatanawiam jak wyeliminowali opóźnienia do akceptowalnego poziomu - no bo jakoś musieli. Gdyby o to nie zadbali, to MID będzie dla AMD topem

- Chiplety w GPU (autor: pwil2 | data: 23/08/23 | godz.: 03:34)

Kwestia czasu, na dopracowanie tych rozwiązań, a wtedy będą mogli robić GPU w 2nm przed konkurencją z małych okruszków krzemu. Średnia półka 1-2 GCD, wyższa 3-6 GCD, a do obliczeń 16 GCD otoczone wieloma MCD w tańszym procesie. A jak będzie wychodzić kolejne PS6/XSX2 to wrzucą chiplet CCD, kilka GCD i otoczą kilkoma MCD otoczone kostkami pamięci na jednym układzie.

- Minaturyzacja przynosi jeszcze lepsze czasy dostępu (autor: Mario1978 | data: 23/08/23 | godz.: 12:41)

ale to chyba zrozumiałe. Przebiegnij 100 metrów a przebiegnij 50 metrów i się dowiesz, w którym wykręciłeś lepszy czas. AMD opracowało architekturę pod chiplety i narazie wszystkie idzie w poziomie. Prawdziwy przełom zacznie się gdy będą oprócz poziomu zapełniać pion. Szybkość połączenia oraz czas dostępu zależy także od miniaturyzacji i odkryć związanych także z dopasowaniem różnych surowców użytych do produkcji takich układów. Do tego w końcu SRAM zostanie zastąpiony czymś szybszym. Dorzućmyu do tego nieulotne pamięci, które też będą mogły wykazać się ultra szybkimi czasami dostępów z wysoką przepustowością. Tylko AMD nie ma zbyt wiele czasu by zarobić jeszcze więcej kasy bo USA swoją polityką wobec Chin się o to postarali myśląc, że nie możliwym jest żeby Chiny dokonały przełomów u siebie. Ale póki mogą jeszcze zarobić na swoich zaawansowanych projektach niech to robią.

|

|

|

|

|

|

|

|

|

D O D A J K O M E N T A R Z |

|

| |

|

Aby dodawać komentarze, należy się wpierw zarejestrować, ewentualnie jeśli posiadasz już swoje konto, należy się zalogować.

|

|

|

|

|

|

|

|

|

|