|

TwojePC.pl © 2001 - 2026

|

|

Wtorek 4 czerwca 2024 |

|

| |

|

Intel Arrow Lake i Lunar Lake, rdzenie Lion Cove i Skymont zapowiedziane

Autor: Zbyszek | źródło: Intel | 20:47 |

(13) |  Intel podczas targów Computex zapowiedział, że jesienią tego roku zadebiutują dwie zupełnie nowe serie procesorów przeznaczone dla komputerów osobistych. Dla lekkich i cienkich laptopów przewidziano procesory o nazwie kodowej Lunar Lake, które trafią na rynek jako Core Ultra serii 200, i prawdopodobnie zastąpią oferowane od ubiegłego roku chipy z serii Meteor Lake (Core Ultra 100). Będą to pierwsze laptopowe procesory Intela posiadające bezpośrednio na podstawce procesora zamontowane pamięć RAM typu LPDDR5X (tuż obok rdzeni krzemowych). Dla komputerów stacjonarnych pojawią się procesory o nazwie kodowej Arrow Lake, które miały trafić na rynek jako Core 15. generacji, ale ostatecznie również dołączą do serii Core Ultra 200. Intel podczas targów Computex zapowiedział, że jesienią tego roku zadebiutują dwie zupełnie nowe serie procesorów przeznaczone dla komputerów osobistych. Dla lekkich i cienkich laptopów przewidziano procesory o nazwie kodowej Lunar Lake, które trafią na rynek jako Core Ultra serii 200, i prawdopodobnie zastąpią oferowane od ubiegłego roku chipy z serii Meteor Lake (Core Ultra 100). Będą to pierwsze laptopowe procesory Intela posiadające bezpośrednio na podstawce procesora zamontowane pamięć RAM typu LPDDR5X (tuż obok rdzeni krzemowych). Dla komputerów stacjonarnych pojawią się procesory o nazwie kodowej Arrow Lake, które miały trafić na rynek jako Core 15. generacji, ale ostatecznie również dołączą do serii Core Ultra 200.

W tym przypadku pojawią się procesory Core Ultra 9 285K i Core Ultra 9 275, Core Ultra 7 265K i Core Ultra 7 255, oraz Core Ultra 5 245K i Core Ultra 5 240, których debiut ma nastąpić w październiku. Najbardziej wydajny Core Ultra 9 285K ma mieć 8 wydajnych rdzeni (8 wątków) i 16 efektywnych rdzeni - łącznie obsługiwał będzie 24 wątki.

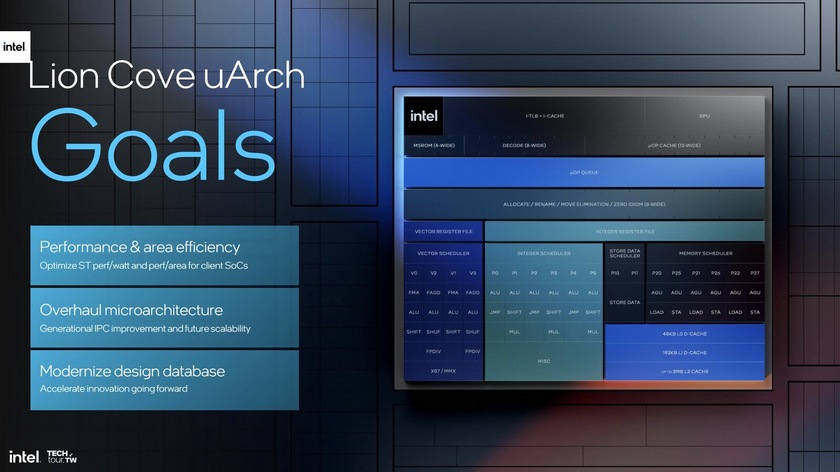

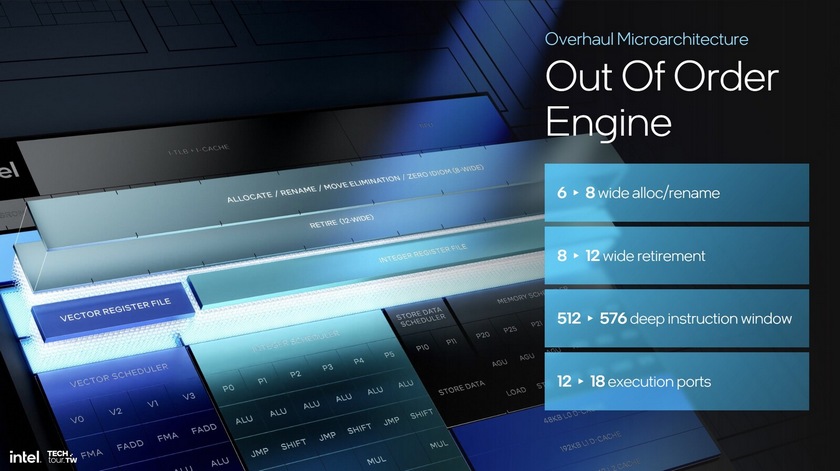

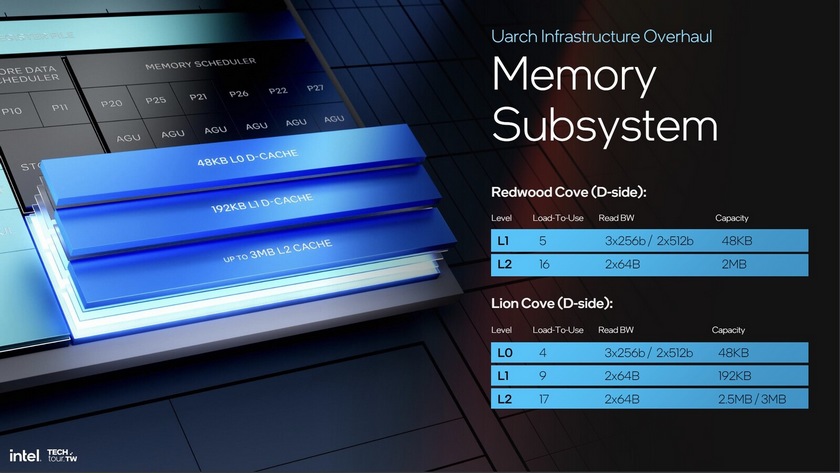

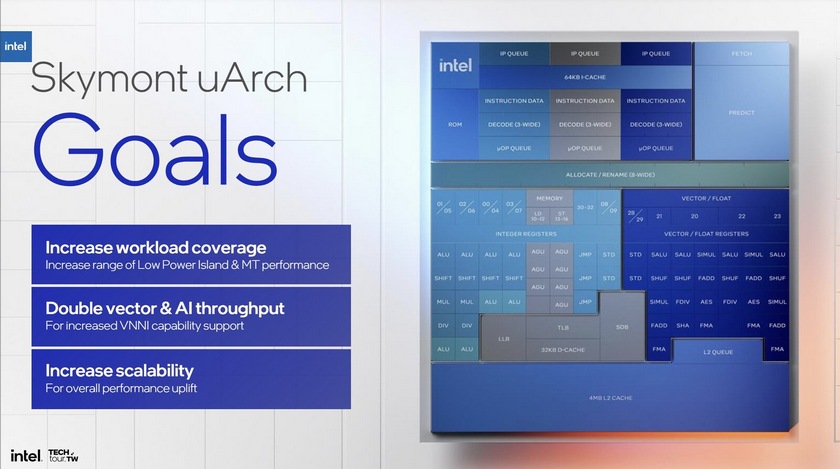

Zarówno Arrow Lake jak i Lunar Lake wykorzystają rdzenie x86 zupełnie nowej generacji - wydajne rdzenie Lion Cove, oraz efektywne rdzenie Skymont. Oba rodzaje rdzeni nie będą się już różnić tak bardzo pod względem wydajności, jak w dotychczasowych procesorach Core 12, 13 i 14 generacji. Co jednak ciekawe - rdzenie Lion Cove i Skymont dla procesorów Lunar Lake mają być produkowane przez TSMC w litografii 3nm, a te same rdzenie dla Arrow Lake przez Intela w litografii 20A. Oznacza to, że końcowe dopracowywanie tych rdzeni w zakresie poprawności parametrów sygnałowo-elektrycznych oraz poprawy osiąganych częstotliwości taktowania musiało być realizowane oddzielnie dla rdzeni wytwarzanych przez TSMC, i oddzielnie dla rdzeni które będą powstawać w litografii Intel 20A (to całkiem różne litografie, wykorzystujące różny typ tranzystorów - FinFET i GaaFET).

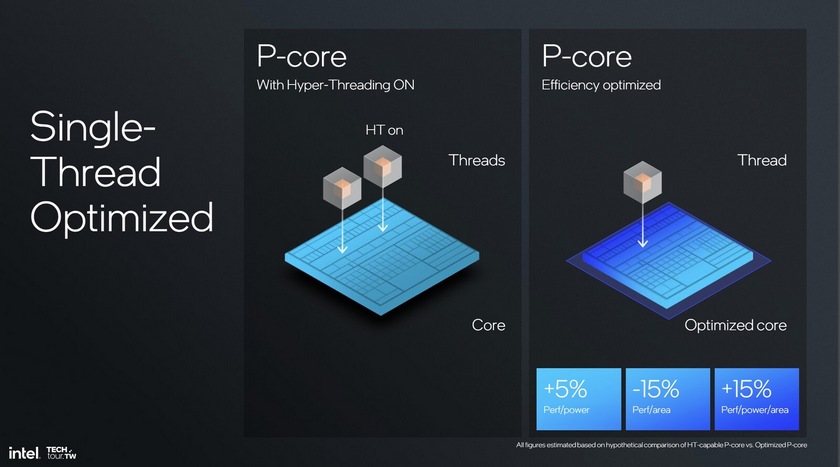

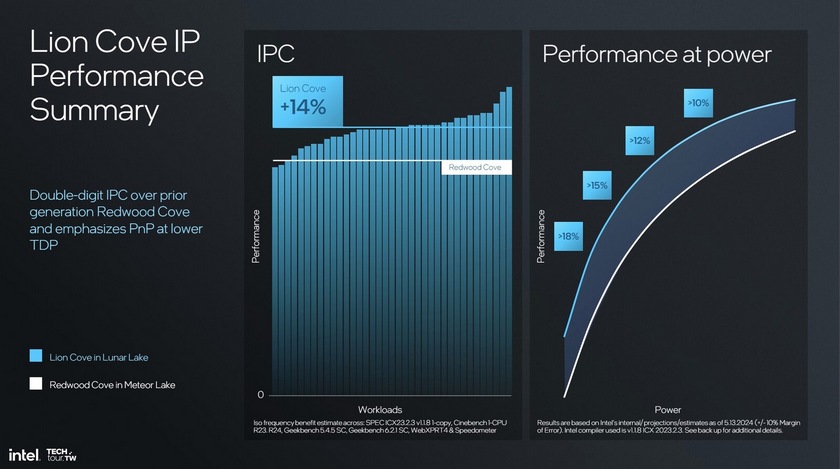

Intel ujawnił, że rdzenie Lion Cove mają o 14 procent większy wskaźnik IPC niż poprzednie Redwood Cove z procesorów Meteor Lake (czyli około 20 procent wyższy niż Golden Cove i Raptor Cove). W odróżnieniu od Golden/Raptor Cove i Redwood Cove, rdzenie Lion Cove nie będą już obsługiwać funkcji HyperThreading, co spowoduje około 15 procentowy spadek wydajności wielowątkowej niż gdyby funkcja HT była w nich dostępna.

Intel tłumaczy to posunięcie względami bezpieczeństwa- brak HT ma wyeliminować możliwość wykrywania jakichkolwiek luk. Jednocześnie utrata tej dodatkowej wydajności jaką oferowała funkcja HyperThreading zostanie zniwelowana przez wzrost IPC - to znaczy nowe rdzenie zaoferują wyższą o kilkanaście procent wydajność jednowątkową, i podobną wielowątkową jak dotychczasowe rdzenie Redwood Cove. Brak wsparcia dla HyperThreadingu ma też powodować niższe zużycie energii elektrycznej.

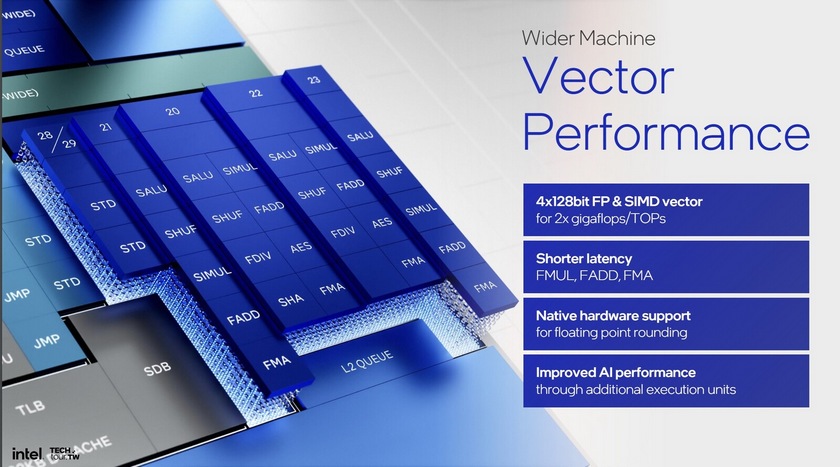

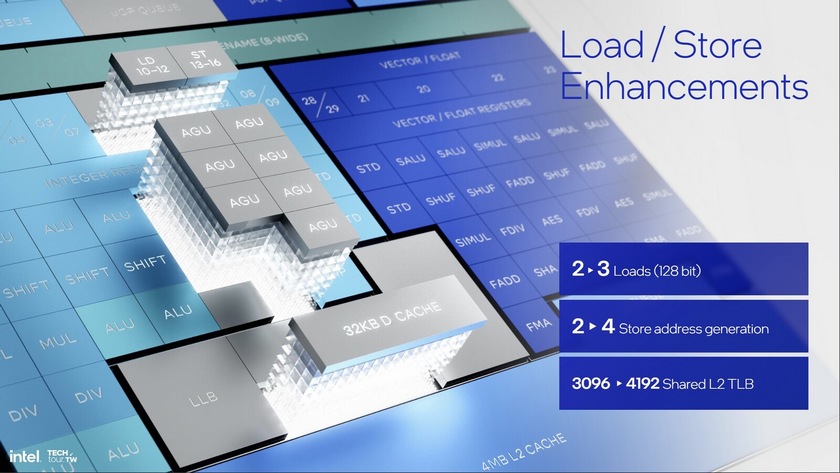

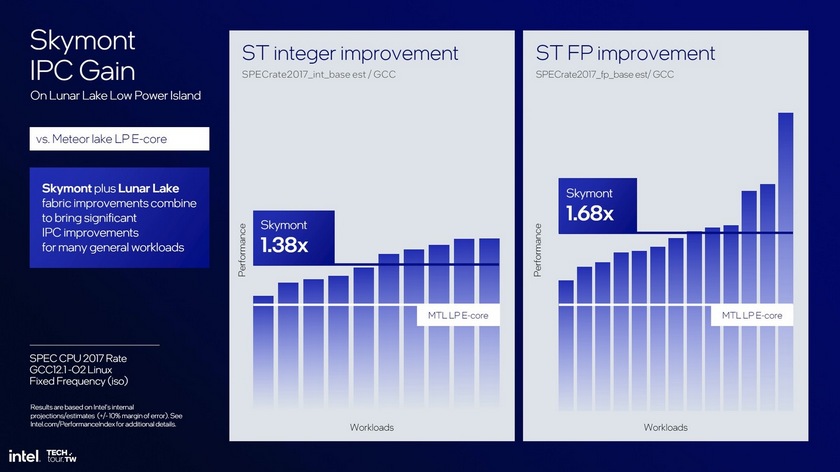

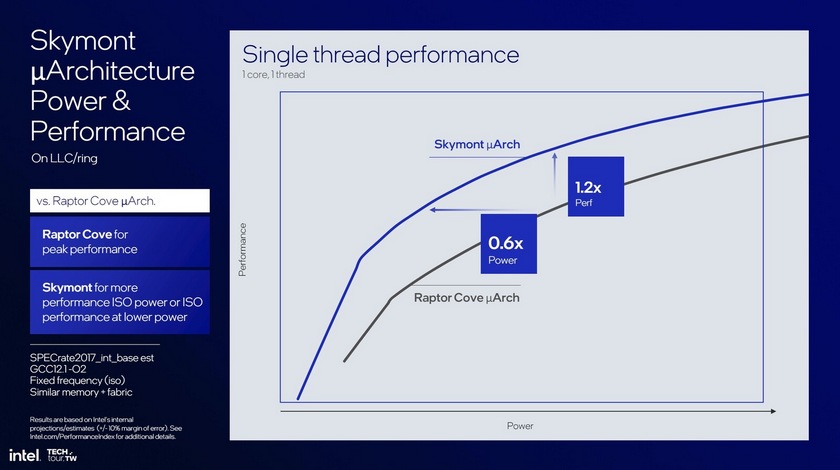

Znacznie większy przyrost wskaźnika IPC przynoszą nowe efektywne rdzenie Skymont - oferują one o 38 procent większy wskaźnik IPC w porównaniu do efektywnych rdzeni Crestmont z procesorów Meteor Lake (i około 50 procent więcej IPC niż efektywne rdzenie Gracemont dotychczasowych procesorów Core 12, 13 i 14 generacji).

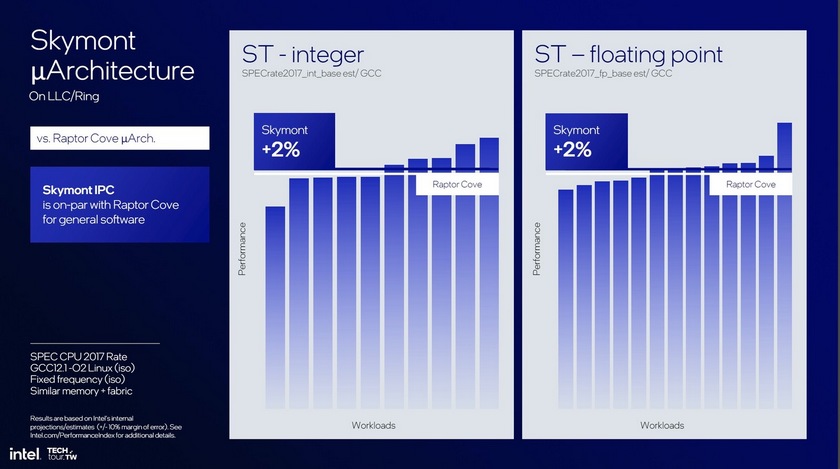

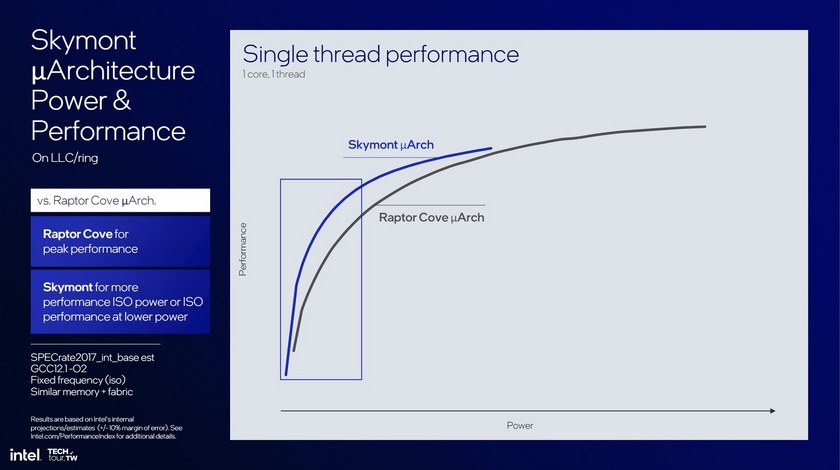

Intel podaje też, że wskaźnik IPC rdzeni Skymont jest o 2 procent wyższy, niż rdzeni Golden i Raptor Cove, czyli wydajnych rdzeni procesorów Core 12, 13 i 14 generacji. Przy czym rdzenie Skymont pobierają mniej energii, ale z drugiej strony osiągają też niższe częstotliwości taktowania, zatem ich sumaryczna wydajność będąca iloczynem IPC i taktowania będzie jednak niższa.

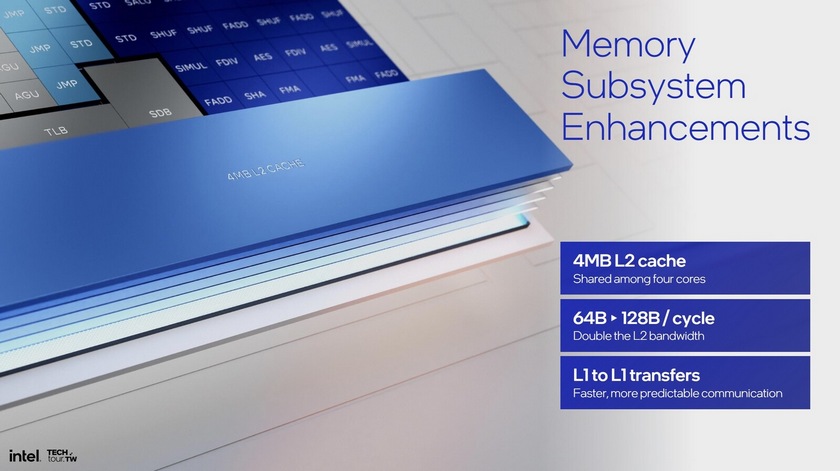

Należy dodać, że rdzenie Skymont mają o 2 procent wyższy wskaźnik IPC niż Raptor Cove i to pomimo tego że cztery takie rdzenie współdzielą jedną pamięć L2 o pojemności 4MB, a każdy rdzeń Raptor Cove miał 2MB własnej pamięci L2. Gdyby dysponowały własną pamięcią L2, ich wskaźnik IPC byłby zapewne o dodatkowe kilka procent wyższy.

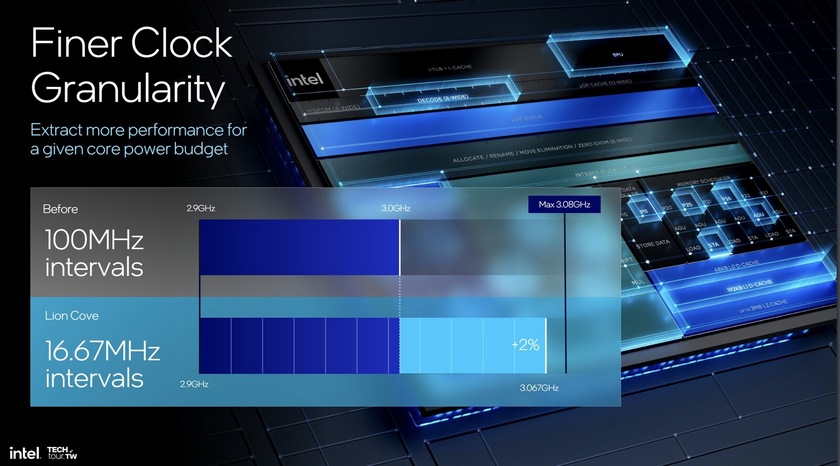

Intel zapowiedział również, że dzięki wielu modyfikacjom z zakresu efektywnosci energetycznej (wprowadzono je głównie do wydajnych rdzeni Lion Cove) procesory desktopowe Arrow Lake będą pobierać już zauważalnie mniej energii niż dotychczasowe Core 12, 13 i 14 generacji.

|

| |

|

|

|

|

|

|

|

|

|

|

K O M E N T A R Z E |

|

| |

|

- czyli sumarycznie (autor: Zbyszek.J | data: 4/06/24 | godz.: 21:45)

Lion Cove z wyższym IPC niż ZEN 5, ale bez obsługi dwóch wątków.

P-Core i E-Core coraz bliższe sobie, ale to wciąż całkowicie różne projekty - jeden rdzeń mający uzyskać wysokie taktowanie, drugi rdzeń trochę niższe iPC, trochę niższe taktowanie i mniejszą zajętość krzemu.

Ciekawe które podejście wygra - Intela czy AMD. AMD bierze po prostu ZEN 5 i robi rdzeń o takiej samej architekturze, ale mając o połowę mniejszy cache L3, uproszczone obwody zasilające, a duża część logiki działa dokładnie tak samo ale jest zmodyfikowana przez oprogramowanie służące do zaprojektowania obwodów wyższej gęstości (nie ma to wpływu na IPC, tylko znów na uzyskiwane maksymalne taktowanie, które jest niższe).

- @01 (autor: GULIwer | data: 4/06/24 | godz.: 22:15)

Tak sobie myślę że intel sobie robi problem z rozdrobnieniem tym że tu bez HT ale do serwerów z HT. Do tego P i E cores. Amd klepie 1 chip i robi od desktopa po serwer. Chociaż chciałbym zobaczyć takie AMD bez HT z 20% wyższą wydajnością 1 wątku, mniejszym zuzyżciem prądu i większym bezpieczeństwem. Takie 8/8 z 3D. Piękna sprawa do gier.

- możliwe (autor: Markizy | data: 5/06/24 | godz.: 06:49)

że intel wymyśla koncepcje HT na nową i stare rozwiązanie wymaga gruntownego przebudowania a na to potrzebują czasu.

Co do rdzeni myślę że pójdą drogą amd, tylko że tutaj inżynierowie muszą się nauczyć kompresować mocniej tranzystory na małej powierzchni. Zaczynają od mniejszego projektu i rozwija go przy okazji zdobywając doświadczenie. Przy okazji może powstać coś ciekawego jak N100. Powód tego jest prosty amd korzysta z rozwiązań TSMC gdzie dla różnych klientów wypracowali różne biblioteki, intel produkuje u siebie i nigdy specjalnie tego nie potrzebował jak miał przewagę.

- @Markizy (autor: Promilus | data: 5/06/24 | godz.: 14:49)

Raczej nie, HT było rozwiązaniem by wykorzystać na drugi wątek nieużywane zasoby przez pierwszy. Czyli jeśli mamy 4 potoki wykonawcze, a pierwszy wątek wykorzystuje 3 to czemu na czwartym nie puścić drugiego wątku - nie będzie to 33% szybsze ze względu na różne inne ograniczenia, ale jednak będzie szybsze niż bez. Teraz wystarczy, że aktualny scheduler zajedwabiście będzie ogarniał zoptymalizowany kod i korzyść z HT znika zupełnie, za to pozostaje niewielka, ale jednak konieczność utrzymania dodatkowej logiki, która zżera prąd choćby czekając na ten drugi wątek... Jak dla mnie jest to jakiś krok, chociaż idą chłopaki ostro w różnych kierunkach i trudno powiedzieć co wyjdzie na dobre. AMD ma ciekawiej, bo ich rdzenie "efektywne" jak na ten moment jeśli chodzi o ficzery nie różnią się niczym oprócz ilości cache więc trochę IPC (i wielkościa - znacznie, i poborem prądu - trochę). Śmiesznie by było gdyby AMD w 3nm zrobiło rdzenie EE z jeszcze mniejszym L2 i w jeszcze większej ilości i z HT - dla 512 rdzeni i 1024 wątków z AVX512 ;)

- Promilus (autor: Markizy | data: 5/06/24 | godz.: 20:24)

wiem jak działa HT, wiec mogą opracowywać nową koncepcje , przypuszczam że ilość potoków wykonawczych może się jednak zwiększać, a to rodzi prawdopodobieństwo że będą wolne jednostki. Teraz mamy zapowiedź 8 ALU. Powód dla którego intel teraz z tego nie korzysta to po prostu problemy z temperaturą i poborem energii.

a

Co do oszczędności powierzchni było to tylko 5% powierzchni, wiec raczej nie z tego powodu zrezygnowali z tego. Natomiast AVX512 przy zen5c będzie działać z niskim raczej zegarem.

- Intel vs AMD (autor: Conan Barbarian | data: 5/06/24 | godz.: 22:46)

Intel pokazuje slajdy a AMD produkty, które łyka wierchuszka rynku IT. Wysłanie bajko-slajderów do Intela było najlepszym posunięciem AMD.

AMD zamierza gonić teraz NVidię bo Intel przysnął w pit-stopie.

- @ up - spokojnie (autor: Zbyszek.J | data: 6/06/24 | godz.: 00:12)

Ostatnie procesory serwerowe AMD i Intela - EPYC 4. gen i Xeon Scalable 4. gen i 5. gen mają rdzenie w zasadzie o identycznym IPC i identycznym taktowaniu. Sytuacja nie spotykana od lat.

Różnica jest taka, że oferta Xeonów (obecnie) kończy się na 60-64 rdzeniach, a AMD ma jeszcze opcję 96-rdzeniową, plus procesory EPYC z dodatkową pamięcią 3D V-Cache. Z drugiej strony Xeony Intela mają większe wsparcie - np. SAP nie daje wsparcia dla swoich systemów jeśli będą uruchomione na serwerach z procesorami EPYC (nie wiadomo dlaczego). A SAP to najbardziej popularny w Europie system typu ERP dla dużych firm

Więc owszem, AMD ma na rynku serwerowym lekką przewagę technologiczną nad Intelem, ale z różnych względów nie przekłada się ona tak jak powinna na przewagę rynkową (w sensie sprzedaż procesorów EPYC nie jest tak dobra jak powinna być).

- @ZbyszekJ (autor: Promilus | data: 6/06/24 | godz.: 05:06)

Jak nie wiadomo o co chodzi to chodzi o pieniądze. ;) Nie jestem zdziwiony bo "od zarania dziejów", a w zasadzie odkąd AMD z brzęczącej koło ucha intela muchy stał się realnym konkurentem intel podpisywał z dużymi graczami umowy na wyłączność. Niektóre były z gruntu nielegalne i po wyjściu na światło dzienne intel musiał za to srogo zapłacić. Inne są skonstruowane tak, że są w pełni legalne. Przykładowo Intel daje podmiotowi X kompy i narzędzia (icc), a ten waliduje soft na sprzęt intela wykorzystując np. specyficzne dla intela rozszerzenia. Intel jest certyfikowany i ma wsparcie, inne platformy nie. Nawet jeśli realnie soft działa. I podmiot X ma rację, postępując inaczej musiałby wspierać użytkowników na platformach na których swojego softu nie walidował i rozwiązywać wszystkie problemy, które z tego wynikają. Stąd supportowane platformy dobiera się starannie i przeprowadza gruntowne testy. A niesupportowane są takie nie bez powodu, nawet jeśli soft ogółem działa. Bo wystarczy że jedna rzecz działać nie będzie i coś się posypie... czemu producent softu miałby być za to odpowiedzialny? Że klient zainstalował to na niewspieranej platformie?

- @7. (autor: pwil2 | data: 6/06/24 | godz.: 16:31)

Za to Oracle przychylniej patrzy w ostatnich latach na AMD:

https://ithardware.pl/...nal_swoj_limit-28160.html

https://www.amd.com/...5-reasons-epyc-oracle-cloud

- @5. (autor: pwil2 | data: 6/06/24 | godz.: 16:33)

5% to było kiedyś. Teraz rzekomo 15%.

Jeśli chodzi o efektywność energetyczną to jednak w 12gen Intela lepsze wyniki (~10%) w budżecie rzędu 65W daje włączone HT.

- LionCove (autor: PCCPU | data: 7/06/24 | godz.: 16:04)

Podobno w ArrowLake może być bardziej dopakowana wersja LionCove. Teraz podobno tworząc docelowy projekt rdzenia usuwają tranzystory dla projektów w których powierzchnia i mniejszy pobór liczy się bardziej. Intel twierdzi że SMT istnieje w pełnym projekcie LionCove ale dla celów LunarLake uznali że energooszczędność i mniejsza powierzchnia jest warta poświęcenia pewnych funkcji/cech architektury.

Inaczej mówiąc do różnych projektów można odchudzić rdzeń np dając mniejszy predyktor, dekoder, ROB czy mniej jednostek wykonawczych.

Np RedwoodCove w GraniteRapids według slajdów Intela(jeśli to nie pomyłka) ma 8 drożny dekoder tak samo jak LionCove. Pytanie czy to ten sam RedwoodCove co w MeteorLake.

Idąc tym tropem w ArrowLake może być bardziej rozbudowany wariant LionCovw z wyższym IPC.

- LionCove (autor: PCCPU | data: 7/06/24 | godz.: 16:17)

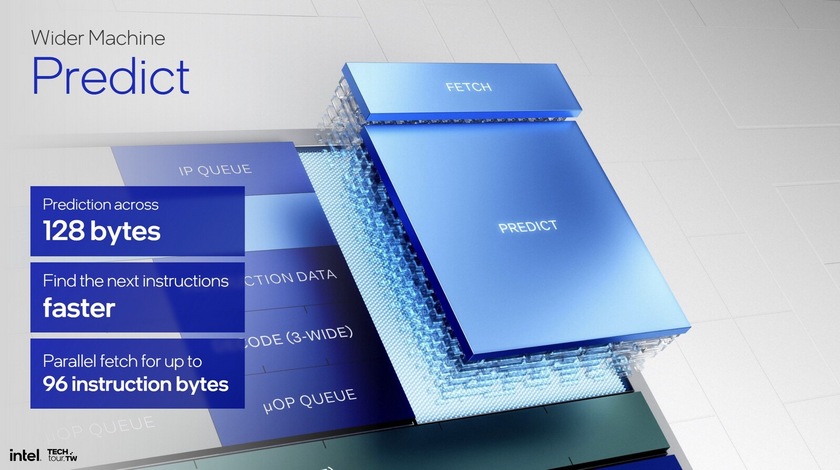

Ciekawostką jest że predyktor jest 8x większy od tego w GoldenCove.

- Edit: (autor: PCCPU | data: 7/06/24 | godz.: 17:32)

Do 8x większy blok predykcji. Pytanie czy w LunarLake jest wariant LionCove z mniejszym blokiem predykcji.

|

|

|

|

|

|

|

|

|

D O D A J K O M E N T A R Z |

|

| |

|

Aby dodawać komentarze, należy się wpierw zarejestrować, ewentualnie jeśli posiadasz już swoje konto, należy się zalogować.

|

|

|

|

|

|

|

|

|

|