|

TwojePC.pl © 2001 - 2026

|

|

Środa 17 lipca 2024 |

|

| |

|

AMD przedstawia szczegóły architektury ZEN 5 i RDNA 3.5

Autor: Zbyszek | źródło: AMD | 19:29 |

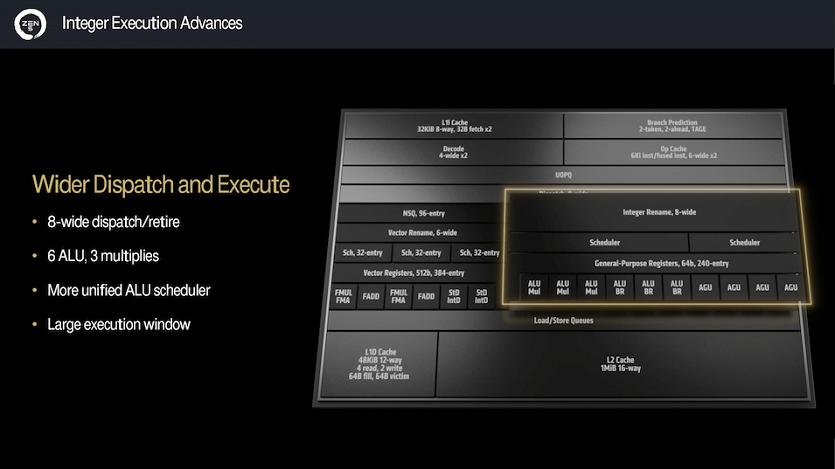

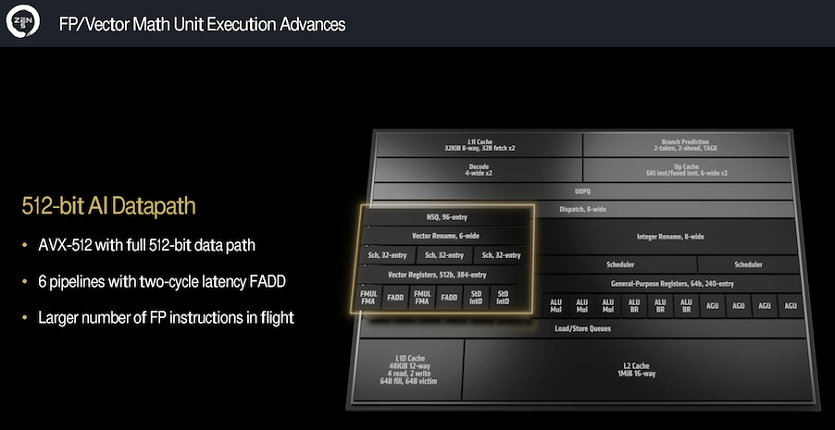

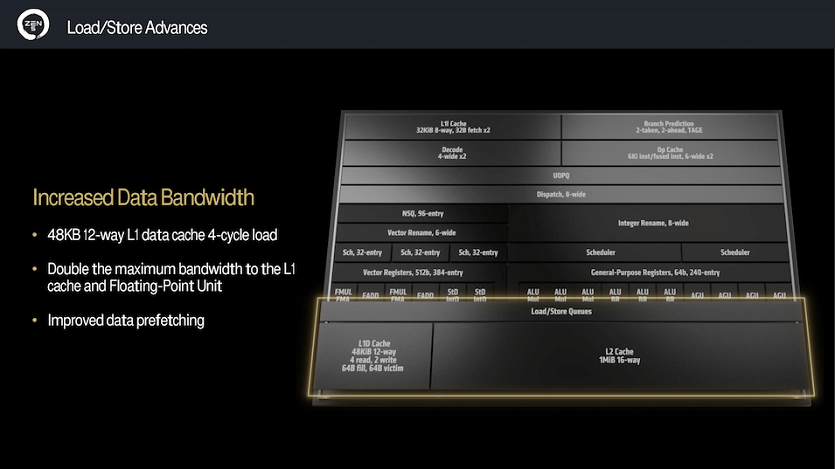

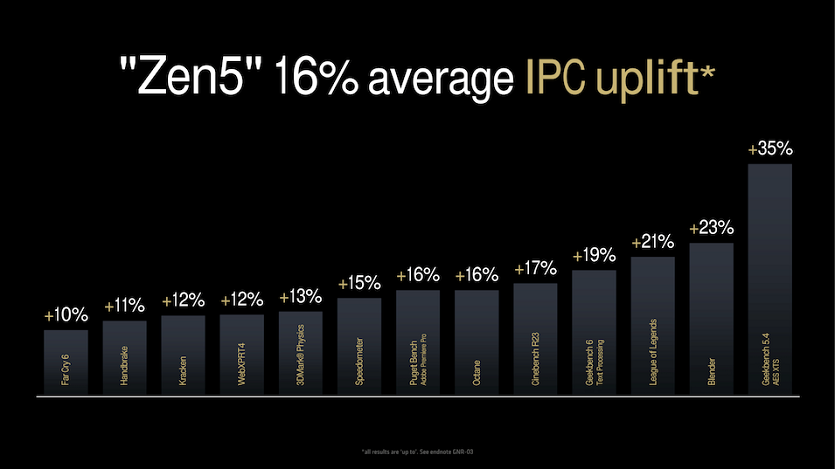

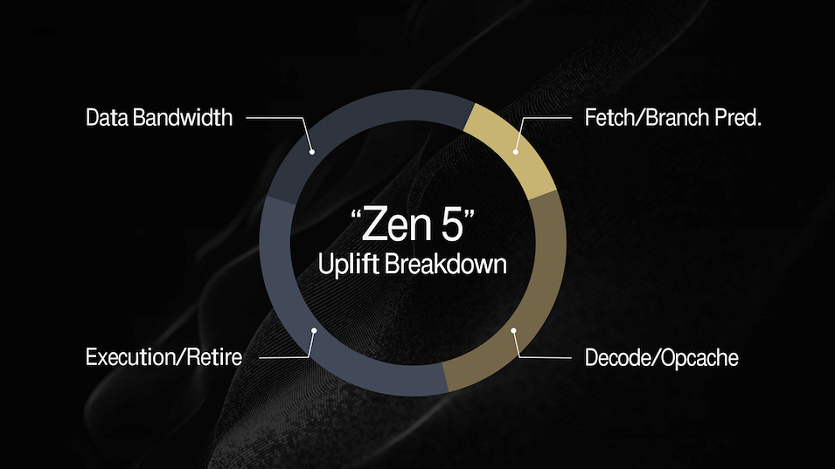

(8) |  Firma AMD zorganizowała wydarzenie o nazwie 2024 Tech Day, w trakcie którego przedstawiono szczegóły architektury ZEN 5 oraz informacje na temat architktury RDNA 3.5. Nowa architektura ZEN 5 ma usprawnioną i bardziej rozbudowaną budowę wewnętrzną. Usprawniono m.in. front-end, system predykcji skoków, zwiększono liczbę potoków wykonawczych, powiększono elementy zapewniające równolegle wykonywanie wielu instrukcji, a także zwiększono wydajność kopiowania danych pomiędzy pamięciami L2 i L1 oraz pomiędzy pamięcią L1 i jednostką zmiennoprzecinkową. Wszystkie wprowadzone zmiany przekładają się na wzrost wskaźnika IPC średnio o 16 procent. Firma AMD zorganizowała wydarzenie o nazwie 2024 Tech Day, w trakcie którego przedstawiono szczegóły architektury ZEN 5 oraz informacje na temat architktury RDNA 3.5. Nowa architektura ZEN 5 ma usprawnioną i bardziej rozbudowaną budowę wewnętrzną. Usprawniono m.in. front-end, system predykcji skoków, zwiększono liczbę potoków wykonawczych, powiększono elementy zapewniające równolegle wykonywanie wielu instrukcji, a także zwiększono wydajność kopiowania danych pomiędzy pamięciami L2 i L1 oraz pomiędzy pamięcią L1 i jednostką zmiennoprzecinkową. Wszystkie wprowadzone zmiany przekładają się na wzrost wskaźnika IPC średnio o 16 procent.

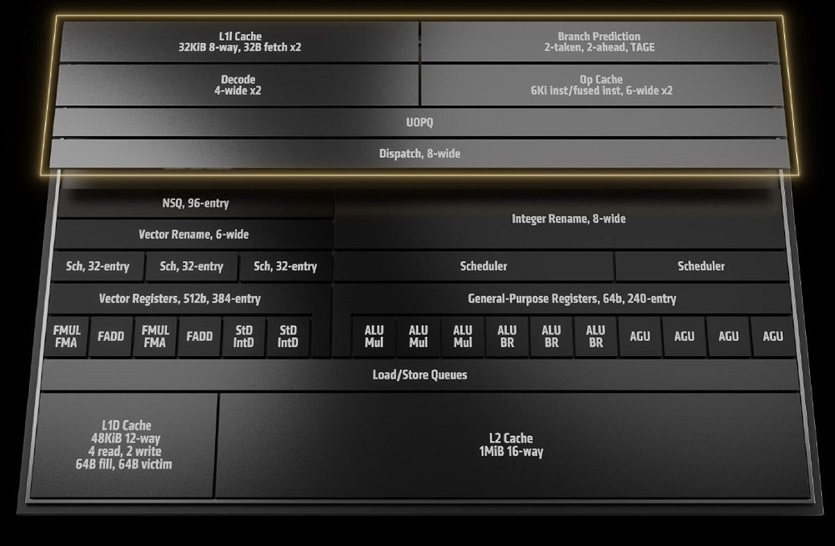

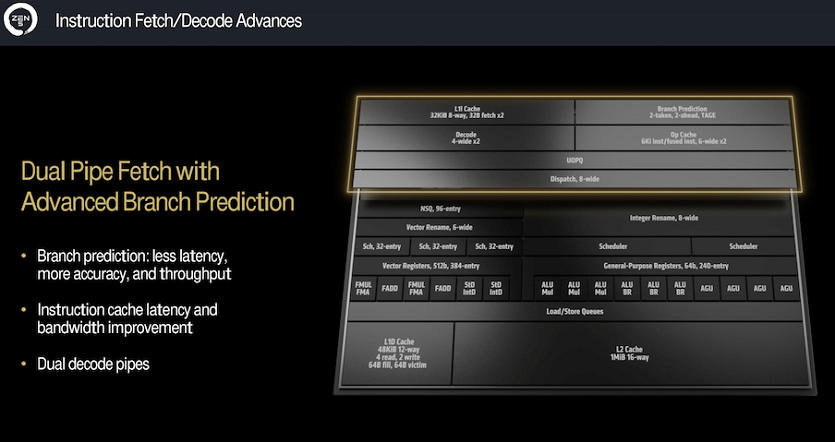

W części front-end rdzeni ZEN 5 znajduje się podwójny czterodrożny dekoder, co jest dość ciekawym rozwiązaniem - prawdopodobnie drugi dekoder włącza się tylko przy pełnym obciążeniu pierwszego, a w innych sytuacjach pozostaje uśpiony, co oszczędza energię. Pamięć L1 dla instrukcji ma taką samą pojemność (32 KB) jak w architekturze ZEN 4, a pamięć L0 dla zdekodowanych mikroinstrukcji mieści 6000 instrukcji, czyli nieco mniej niż w architekturze ZEN 4, ale ma wyższą przepustowość. Ogólnie front-end może dostarczyć do jednostek wykonawczych 8 zdekodowanych mikroinstrukcji, zamiast sześciu jak we wszystkich poprzednich architekturach ZEN.

W części stałoprzecinkowej zastosowano 10 potków wykonawczych, w których znajduje się sześć jednostek ALU i cztery jednostki AGU. Jest to istotny wzrost - ZEN 4 miał cztery jednostki ALU, i trzy jednostki AGU. Część zmiennoprzecinkowa ma podobną 6-potokową budowę jak w architekturze ZEN 4, zastosowano jednak zmodyfikowane schedulery, skrócono opóźnienie wykonywania operacji dodawania z 3 cykli do 2 cykli zegara, oraz dwukrotnie zwiększono wydajność przetwarzania instrukcji AVX-512.

Część back-end ma całkowicie zmodyfikowaną pamięć L1 dla danych - jej pojemność wzrosła z 32 KB do 48 KB, a przepustowość do pamięci L2 i do jednostki zmiennoprzecinkowej wzrosła dwukrotnie. Powiększono też kolejki Load/Store oraz usprawniono prefetching.

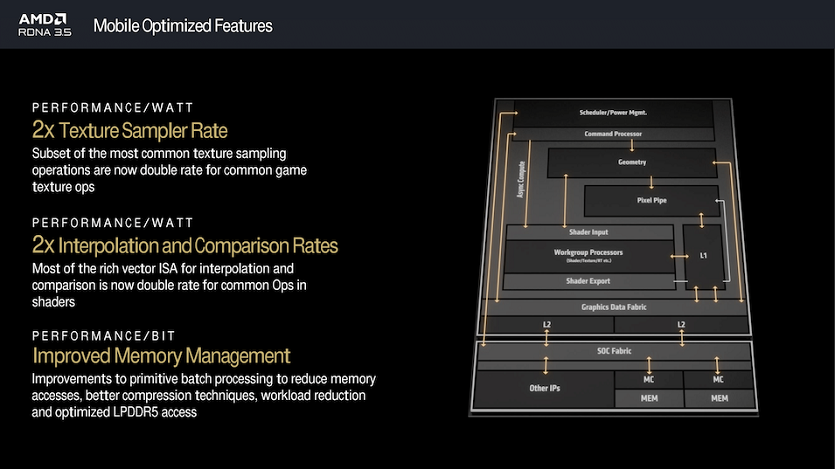

Przedstawiono też po krótce informacje na temat architektury RDNA 3.5. Według AMD RDNA 3.5 to architektura RDNA 3 zoptymalizowana pod kątem niższego zużycia energii, a wszystkie wprowadzone modyfikacje skupiały się wyłącznie na wyższej wydajności na wat. RDNA 3.5 będzie stosowana wyłączone w zintegrowanych układach graficznych przeznaczonych dla komputerów przenośnych.

|

| |

|

|

|

|

|

|

|

|

|

|

K O M E N T A R Z E |

|

| |

|

- ogólnie (autor: Shark20 | data: 18/07/24 | godz.: 01:13)

jak na to co tam pozmieniali to uzyskany wzrost IPC mógłby być wyższy niż te 16%. ZEN 3 miał mniej zmian, a wzrost IPC miał +19%, plus wzrost częstotliwości taktowania o 300-400 MHz.

Ale potencjał dalszego wzrostu IPC może być dość duży. To jest taka architektura jak ZEN 1 - całkiem nowa, i ZEN 6 oraz ZEN 7 będą z dość dużym prawdopodobieństwme jej fajnymi rozwinięciami.

- Pamiętacie jak w czasach Skylake (autor: pwil2 | data: 18/07/24 | godz.: 05:55)

Intel twierdził, że już praktycznie doszli do ściany IPC?

- pwil2 (autor: Markizy | data: 18/07/24 | godz.: 09:10)

chyba im chodziło o 4 drożne dekodery.

Shark20

Prawdopodobnie będą teraz poprawiać tą architecture przez zen6 i zen7 po czym zen 8 dostanie coś nowego.

- @ pwil2 (autor: Shark20 | data: 18/07/24 | godz.: 21:37)

ZEN 4 i Golden/Raptor Cove mają o 39-40% wyższy wskaźnik IPC niż Skylake. A teraz ZEN 5 ma o ~60-61% wyższy wskaźnik IPC niż Skylake. Trzeba by jeszcze porównać liczbę tranzystorów rdzenia Skylake i jednego rdzenia ZEN 5, bo pewnie jest tak, że te dodatkowe 60% IPC wcale nie kosztowało o 60% więcej tranzystorów w rdzeniu, tylko znacznie więcej.

- no i ogólnie (autor: Shark20 | data: 18/07/24 | godz.: 23:10)

ZEN 5 ma IPC o około 65% wyższe niż ZEN 1

- @Markizy @Shark20 (autor: pwil2 | data: 19/07/24 | godz.: 01:23)

To było w czasach, gdy utknęli na 14nm, a nie spodziewali się, że konkurencja czymś zaskoczy. To wyglądało jak tłumaczenie, że wyścig się skończył, a teraz będziemy zmieniać laptopy, bo nowe wifi weszło albo kodek.

Oni potrzebowali nowej architektury, którą następnie będzie można rozwijać. Ale to 5 lat pracy i miliardy wydane na konkurowanie samemu ze sobą (jak się wtedy wydawało).

- c.d. (autor: pwil2 | data: 19/07/24 | godz.: 01:29)

Intel zaskoczony ZEN dopiero wtedy szukał zespołu, który zacznie pracować nad nową architekturą.

AMD wyciągnęło wnioski i równolegle zawczasu opracowywało architekturę ZEN5, którą będą później mogli ulepszać przez kolejnych kilka generacji dokładając tu i tam po trochu.

- @ up (autor: Shark20 | data: 20/07/24 | godz.: 11:51)

oni mieli projekt nowszych architektur, ale nie mieli litografii do ich produkcji i odgrzewali Skylake.

Ice Lake (2019 rok) to architektura o dwie generacje nowsza niż Skylake. Pominęli jedną.

Skylake (2015)

Cannon Lake = Skylake w 10nm = ten sam IPC

pominięta architektura (8-10% wzrostu IPC ponad Skylake)

Sunny Cove (2019) - dwa kroki w przód, wzrost IPC o 18%

|

|

|

|

|

|

|

|

|

D O D A J K O M E N T A R Z |

|

| |

|

Aby dodawać komentarze, należy się wpierw zarejestrować, ewentualnie jeśli posiadasz już swoje konto, należy się zalogować.

|

|

|

|

|

|

|

|

|

|