|

TwojePC.pl © 2001 - 2026

|

|

Poniedziałek 17 lutego 2025 |

|

| |

|

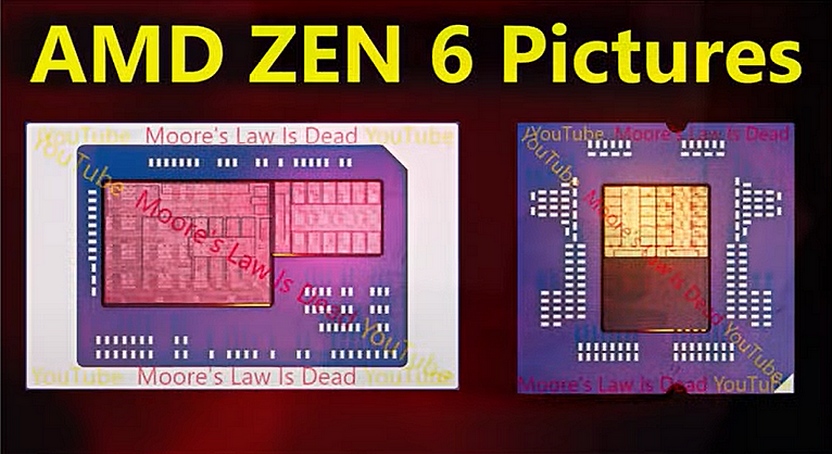

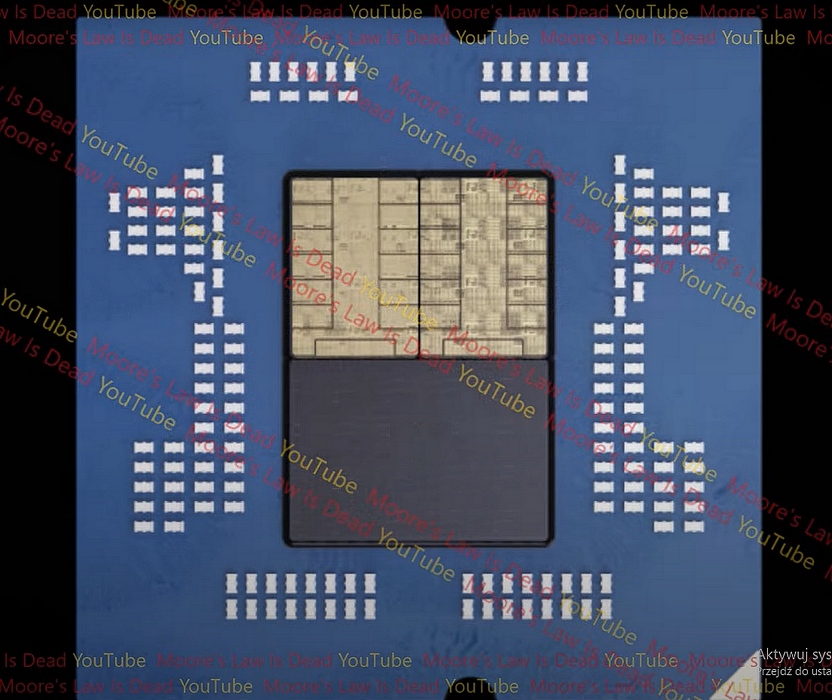

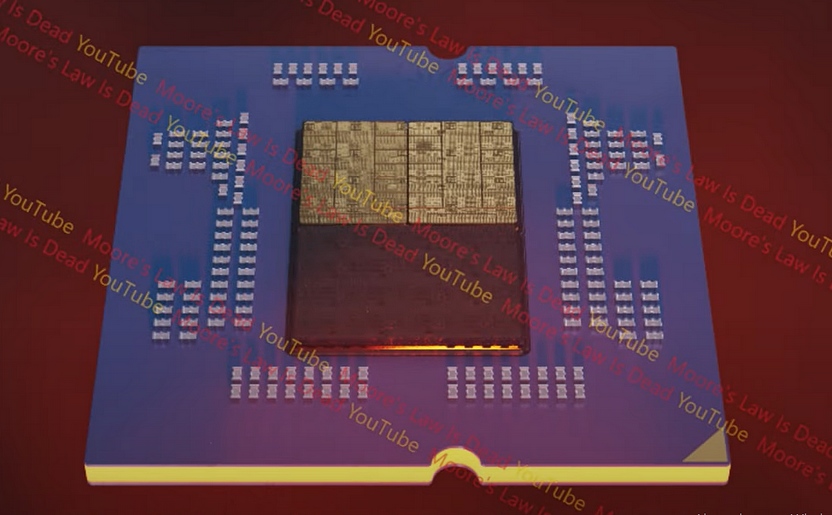

Procesory Ryzen Olympic Ridge otrzymają do 24 rdzeni ZEN 6

Autor: Zbyszek | źródło: Moore Law Is Dead | 18:58 |

(6) |  Kanał Moore Law Is Dead, znany ze sprawdzających się informacji podał, że jest już całkowicie pewne, że po raz pierwszy od kilku lat firma AMD zdecyduje się zwiększyć liczbę rdzeni z swoch procesorach konsumenckich. Ich następna generacja dla podstawki AM5 o nazwie kodowej Olympic Ridge ma otrzymać do 24 rdzeni ZEN 6, umieszczonych w dwóch chipletach CCD, po 12 rdzeni w każdym z nich. Nowe chiplety CCD będą wytwarzane w litografii N3E firmy TSMC, i będą połączone z całkowicie nowym chipletem IOD, produkowanym w litografii 5nm i wyposażonym w jednostkę NPU (Neural Processing Unit). Kanał Moore Law Is Dead, znany ze sprawdzających się informacji podał, że jest już całkowicie pewne, że po raz pierwszy od kilku lat firma AMD zdecyduje się zwiększyć liczbę rdzeni z swoch procesorach konsumenckich. Ich następna generacja dla podstawki AM5 o nazwie kodowej Olympic Ridge ma otrzymać do 24 rdzeni ZEN 6, umieszczonych w dwóch chipletach CCD, po 12 rdzeni w każdym z nich. Nowe chiplety CCD będą wytwarzane w litografii N3E firmy TSMC, i będą połączone z całkowicie nowym chipletem IOD, produkowanym w litografii 5nm i wyposażonym w jednostkę NPU (Neural Processing Unit).

Jeśli chodzi o nazewnictwo, AMD ma dodać do nazwy nowych Ryzenów dopisek "AI", podobnie jak w przypadku ostatnich procesorów dedykowanych dla komputerów przenośnych.

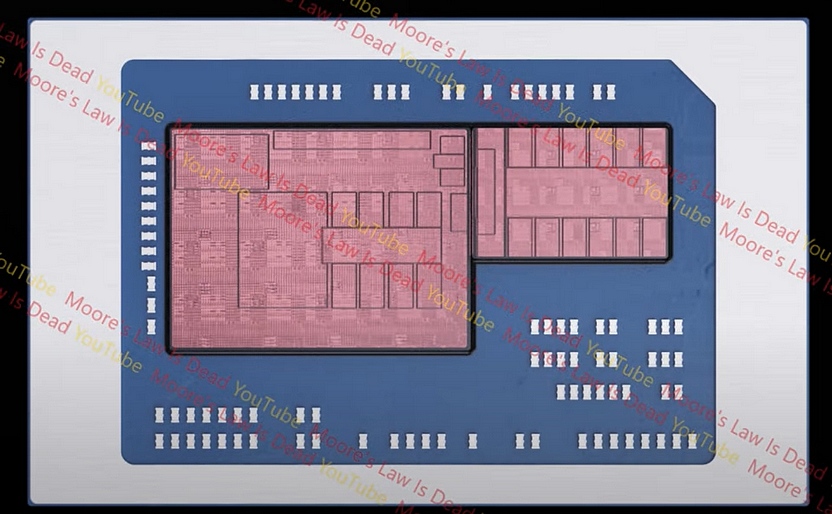

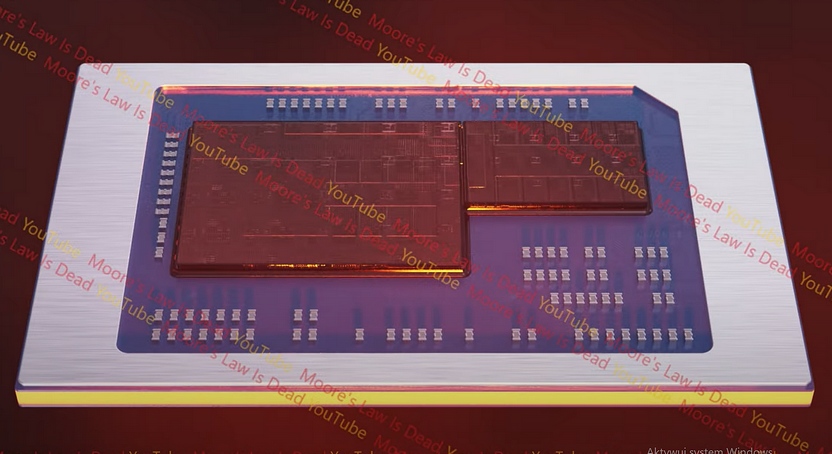

Autorzy kanału Moore Law Is Dead twierdzą też, że mieli już możliwość zobaczenia próbek inżynierskich przyszłych procesorów oraz dokładnych fotografii nowych chipletów CCD oraz IOD, i na tej podstawie przygotowali renderowane grafiki przedstawiające wygląd przyszłych desktopowych procesorów Olympic Ridge oraz laptopowych procesorów Medusa Point. Prezentujemy je poniżej.

|

| |

|

|

|

|

|

|

|

|

|

|

K O M E N T A R Z E |

|

| |

|

- Czekam na przeciek o następcy Stix Halo (autor: Zic | data: 17/02/25 | godz.: 22:55)

Ze względu na RDNA4 czy pojawi się coś więcej niż 40CU.

- Zen6 (autor: Conan Barbarian | data: 18/02/25 | godz.: 18:34)

Gdyby Intel nie leżał na deskach, to byłoby 16c na CCD; a tak to jeszcze premierę przesuną zdrowo.

- @2. (autor: pwil2 | data: 19/02/25 | godz.: 15:19)

Zawsze mogą być 3xCCD. Nie ma sensu pchać więcej rdzeni na CCD, jeśli większość nie odczuje zysku z ponad 8 wydajnych rdzeni o łącznej wydajności 12 dotychczasowych rdzeni ZEN4.

- @pwil2 (autor: rainy | data: 19/02/25 | godz.: 16:41)

Moim zdaniem, konfiguracja 3x12 byłaby nawet gorsza niż 2x16, choć w obydwu przypadkach problem byłby podobny: jak "wykarmić" taką liczbę rdzeni za pomocą dwukanałowego kontrolera pamięci DDR5.

- @4. (autor: pwil2 | data: 20/02/25 | godz.: 00:51)

Więcej rdzeni to odpowiednio więcej cache np. 3x48MB.

48MB L3 może dostać bonusa w grach. 6-16c z 64MB L3 w jednym kawałku jeszcze lepsze, ale przy uzysku 90% szkoda byłoby z tego ciachać wersje docelowo 6c, 8c... A głównym atutem chipletów miało być to, że niewiele się marnuje i opłaca się kupować u TSMC dość świeżą litografię.

- c.d. (autor: pwil2 | data: 20/02/25 | godz.: 00:54)

Ciekawą opcją byłoby wykorzystanie X3D jako współdzielonego między różne CCD cache L4.

|

|

|

|

|

|

|

|

|

D O D A J K O M E N T A R Z |

|

| |

|

Aby dodawać komentarze, należy się wpierw zarejestrować, ewentualnie jeśli posiadasz już swoje konto, należy się zalogować.

|

|

|

|

|

|

|

|

|

|