|

TwojePC.pl © 2001 - 2026

|

|

Środa 27 sierpnia 2025 |

|

| |

|

Do sieci trafiły diagramy architektury UDNA

Autor: Wedelek | źródło: VideoCardZ | 06:17 |

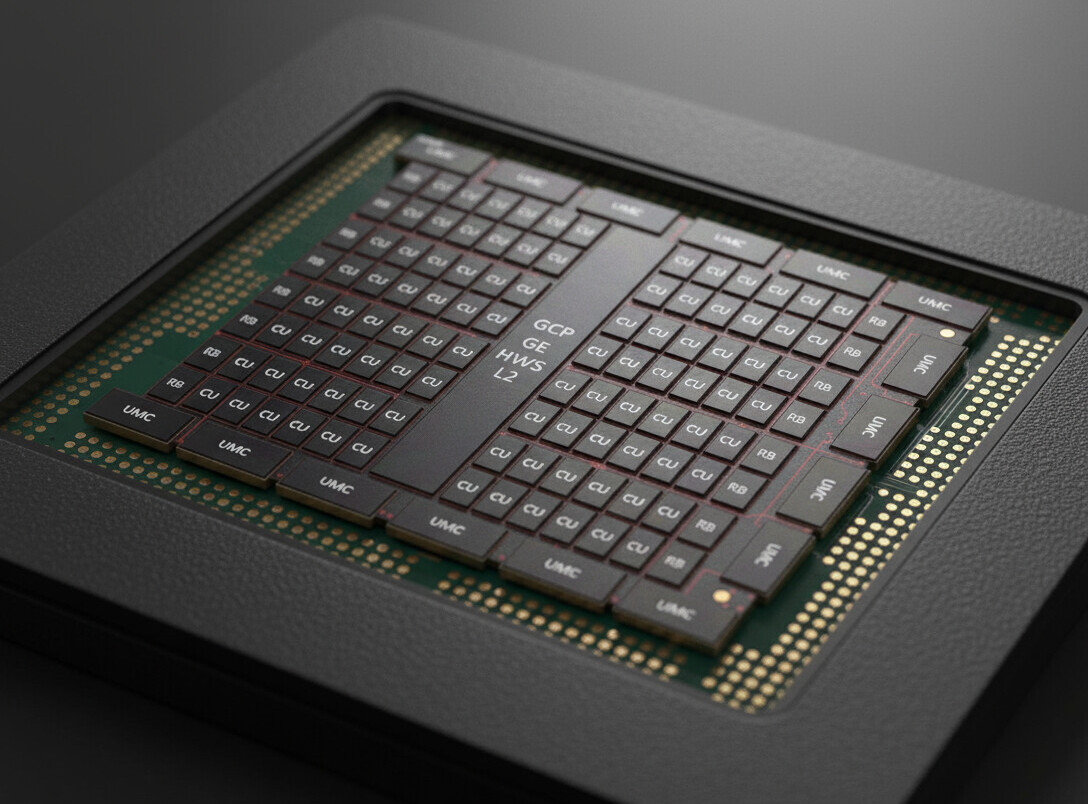

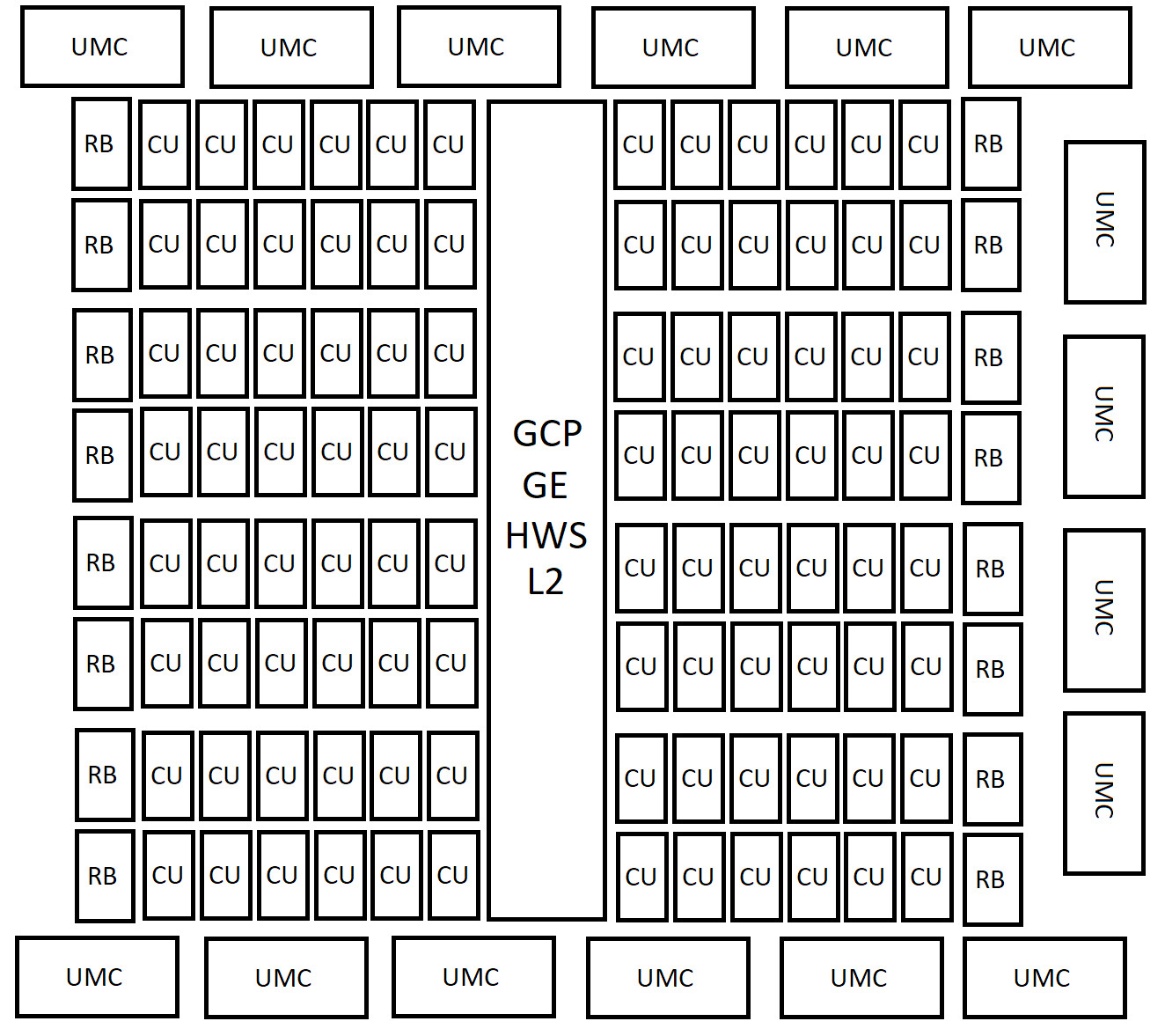

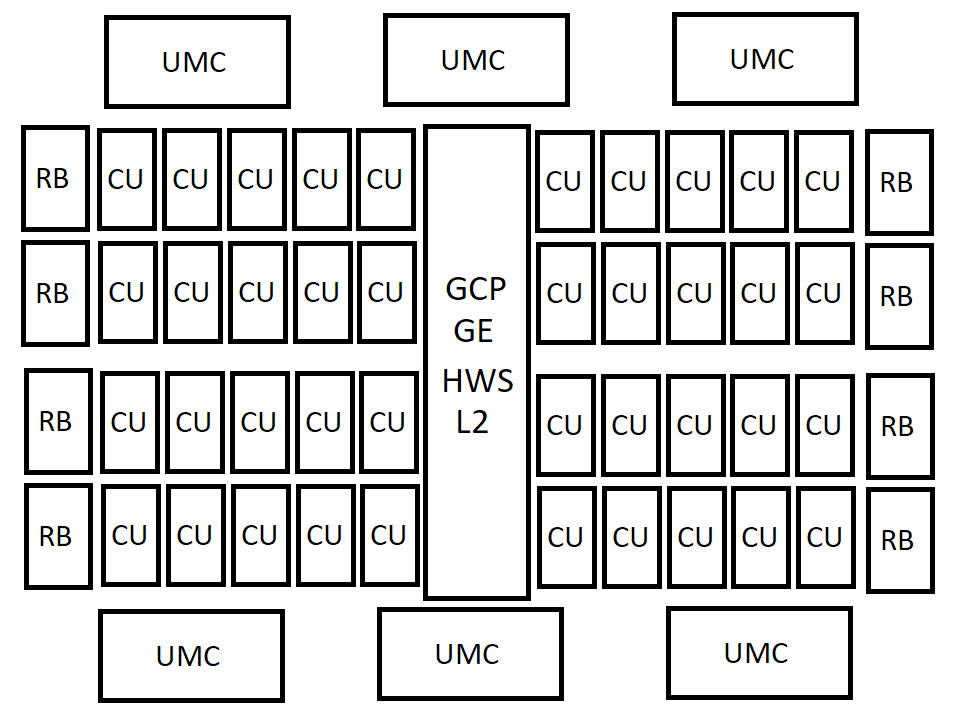

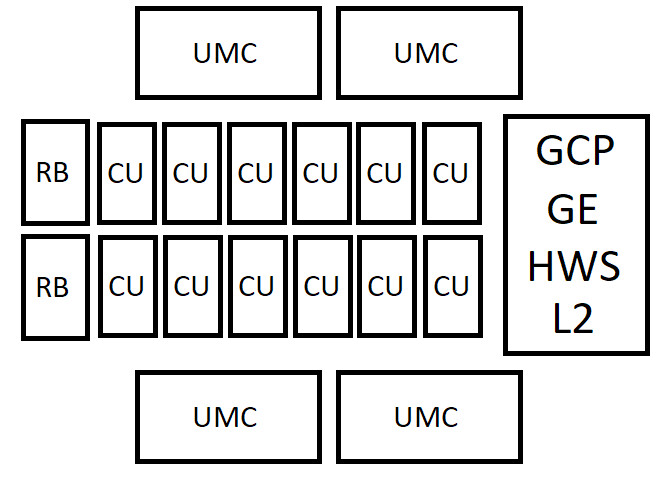

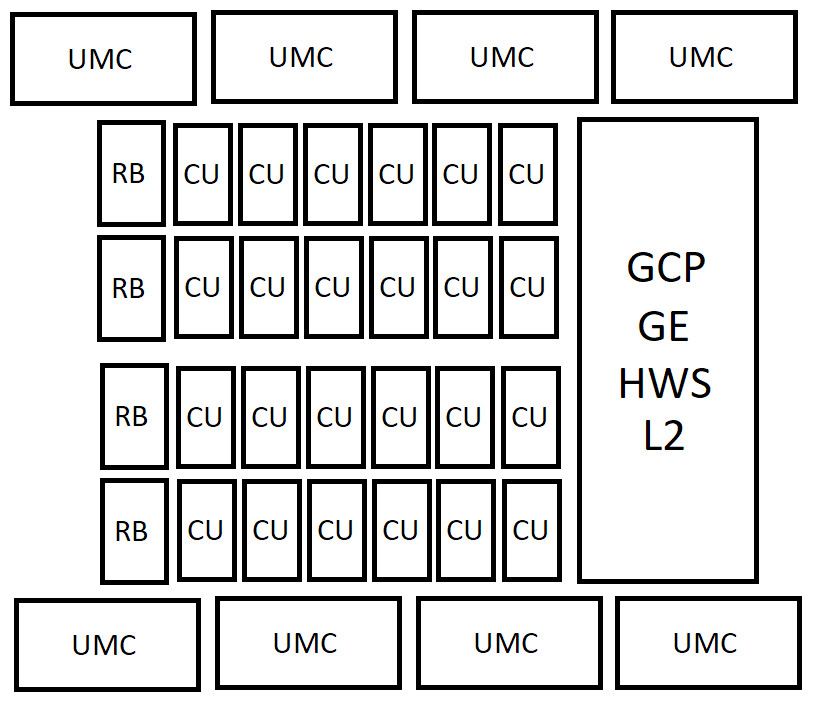

(3) |  Znany użytkownik @Kepler_L2 opublikował w sieci diagramy blokowe układów GPU na bazie nowej mikroarchitektury AMD UDNA. Widzimy na nich cztery rodzaje rdzeni GPU, a największy z nich ma się składać z 96 jednostek obliczeniowych. Grafiki pokazują bloki i silniki shaderów, z których każdy zawiera kilka jednostek obliczeniowych oraz własny backend renderujący. Silniki te są połączone z centralnym blokiem SoC, który obejmuje silnik graficzny, sprzętowe schedulery, współdzieloną pamięć podręczną L2 i jednostki dodatkowe. Znany użytkownik @Kepler_L2 opublikował w sieci diagramy blokowe układów GPU na bazie nowej mikroarchitektury AMD UDNA. Widzimy na nich cztery rodzaje rdzeni GPU, a największy z nich ma się składać z 96 jednostek obliczeniowych. Grafiki pokazują bloki i silniki shaderów, z których każdy zawiera kilka jednostek obliczeniowych oraz własny backend renderujący. Silniki te są połączone z centralnym blokiem SoC, który obejmuje silnik graficzny, sprzętowe schedulery, współdzieloną pamięć podręczną L2 i jednostki dodatkowe.

Po stronie pamięci mamy maksymalnie szesnaście zunifikowanych kontrolerów, każdy o szerokości 32 bitów, co razem daje magistralę o przepustowości 512-bit. Przy zastosowaniu sześciu jednostek obliczeniowych (CU) na silnik (Shader Engine), daje nam to wartość 96 jednostek obliczeniowych w TOPowym modelu. Z kolei w nieco słabszej odmianie mamy mieć do czynienia z konfiguracją 8x5 co przekłada się na 40 jednostek CU.

Widzimy też projekty z 24 i 12 jednostkami CU zbudowane z mniejszych macierzy i mniejszej liczby kontrolerów. Przykładowo wersja z 24 jednostkami CU ma mieć do ośmiu kontrolerów pamięci, co może oznaczać różne szerokości szyny, w zależności od tego, czy całość korzysta z pamięci GDDR, czy LPDDR5X lub pochodnych.

Wyciek wspomina także o możliwości zastosowania w TOPowym modelu znacznie większej pamięci podręcznej Infinity Cache.

Ciekawym szczegółem jest też sugestia, że w modelach kart przygotowanych z myślą o centrach danych CU miałyby do dyspozycji więcej pamięci podręcznej. Widać też, że AMD bardzo mocno stawia nie tylko na unifikację RDNA i CDNA, ale też łatwą skalowalność. Swoją drogą już przy RDNA4 AMD chwaliło się modułowością swojej architektury, o czym pisaliśmy niedawno na łamach TPC.

|

| |

|

|

|

|

|

|

|

|

|

|

K O M E N T A R Z E |

|

| |

|

- to teraz ciekawe które z tych elementów na diagramach będą na wspólnym krzemie (autor: Qjanusz | data: 27/08/25 | godz.: 15:41)

i czy IC będzie montowane pod krzemem jak w Ryzenach

- nie bardzo (autor: Markizy | data: 31/08/25 | godz.: 20:48)

widzę sens wydawanie układów z magistralą pamięci 512bit, 384 bitowa magistrala wydaje się być bardziej przystępna dla graczy. Bardziej rozbudowana magistrala podnosi koszty całego układu jak co nie nie ma większe zastosowania dla użytkownika.

Na tej podstawie mogą stworzyć 4 różne układy przy wykorzystaniu kości 2 i 3GB GDDR7.

384bit 72CU 36GB i słabsza 66/64CU 24GB

256bit 48CU 24GB i słabsza 42/42CU 16GB

128bit 24CU 12GB i słabsza 18/16CU 8GB

oraz

64Bbit 12CU 8GB/6GB, która głównie by zapewniała wsparcie wielu monitorów i nowe kodeki do filmów przy czym odświeżana raz na każdą generacje pamięci (no chyba żeby te pamięci panowały tak długo jak gddr5 to szybciej) i z TDP poniżej 75W.

Przy takim podziale słabsze karty byłby by tylko uzupełnieniem dla oferty, natomiast 128bit 8GB można by od razu przekierować od OEM.

- @up (autor: piwo1 | data: 4/09/25 | godz.: 06:09)

dodatkowe 50zl na plytce na szersza szyne danych to zaden koszt przy cenach 5tys zl za karte. kwestia by na tle rywala wypadac lepiej a bedzie mialo to sens.

|

|

|

|

|

|

|

|

|

D O D A J K O M E N T A R Z |

|

| |

|

Aby dodawać komentarze, należy się wpierw zarejestrować, ewentualnie jeśli posiadasz już swoje konto, należy się zalogować.

|

|

|

|

|

|

|

|

|

|