|

TwojePC.pl © 2001 - 2026

|

|

Środa 12 listopada 2025 |

|

| |

|

AMD dzieli się szczegółami na temat Zen 6 i Zen 7

Autor: Wedelek | źródło: AMD | 05:23 |

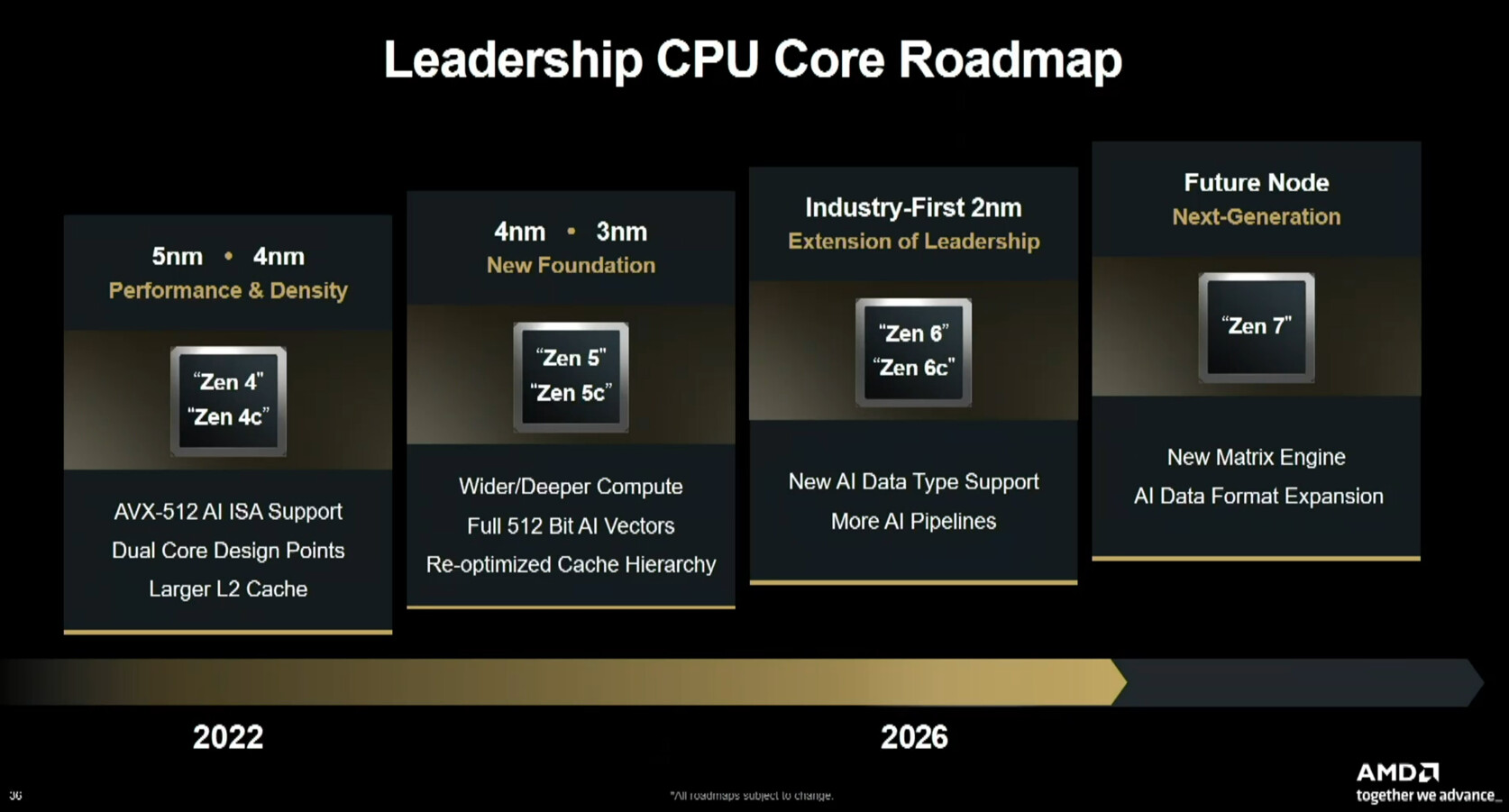

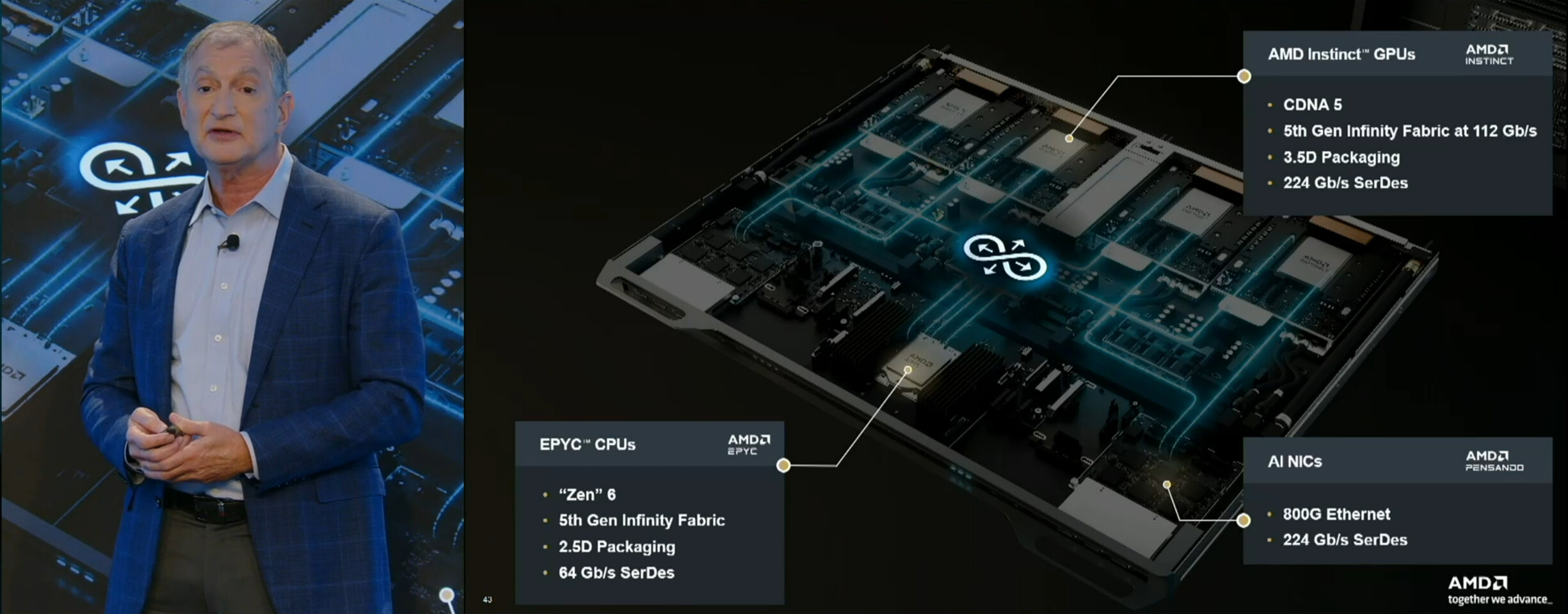

(24) |  Podczas prezentacji przeznaczonej dla inwestorów AMD zaprezentowało zaktualizowany plan wydawniczy na najbliższe lata. Dowiedzieliśmy się z niego między innymi, że Zen 6 pojawi się na rynku w przyszłym roku, a bazujące na nim CPU będą wykonywane w procesie technologicznym 2 nm od TSMC. Nowa mikroarchitektura zmaterializuje się w postaci dwóch rodzajów rdzeni: Zen 6 i Zen 6C, zoptymalizowanych odpowiednio pod kątem wysokiej wydajności i energooszczędności. Według dyrektora technicznego AMD, Marka Papermastera, Zen 6 zapewni wyższy współczynnik IPC (mówi się o +8% względem Zen 5) i lepszą wydajność, również w przypadku AI między innymi dzięki dodatkowym potokom obliczeniowym. Podczas prezentacji przeznaczonej dla inwestorów AMD zaprezentowało zaktualizowany plan wydawniczy na najbliższe lata. Dowiedzieliśmy się z niego między innymi, że Zen 6 pojawi się na rynku w przyszłym roku, a bazujące na nim CPU będą wykonywane w procesie technologicznym 2 nm od TSMC. Nowa mikroarchitektura zmaterializuje się w postaci dwóch rodzajów rdzeni: Zen 6 i Zen 6C, zoptymalizowanych odpowiednio pod kątem wysokiej wydajności i energooszczędności. Według dyrektora technicznego AMD, Marka Papermastera, Zen 6 zapewni wyższy współczynnik IPC (mówi się o +8% względem Zen 5) i lepszą wydajność, również w przypadku AI między innymi dzięki dodatkowym potokom obliczeniowym.

Nieoficjalnie mówi się też o nowej budowie chipletów – każdy ma mieć po maksymalnie 12 rdzeni, co w przypadku modeli desktopowych da nam maksymalnie 24 rdzenie a w układach mobilnych 22 rdzenie. Do tego dojdzie obsługa zegarów 6 GHz, lepszy kontroler pamięci, nowe połączenia mostkowe LSI oraz, w przypadku niektórych CPU, usprawniona pamięć V-Cache.

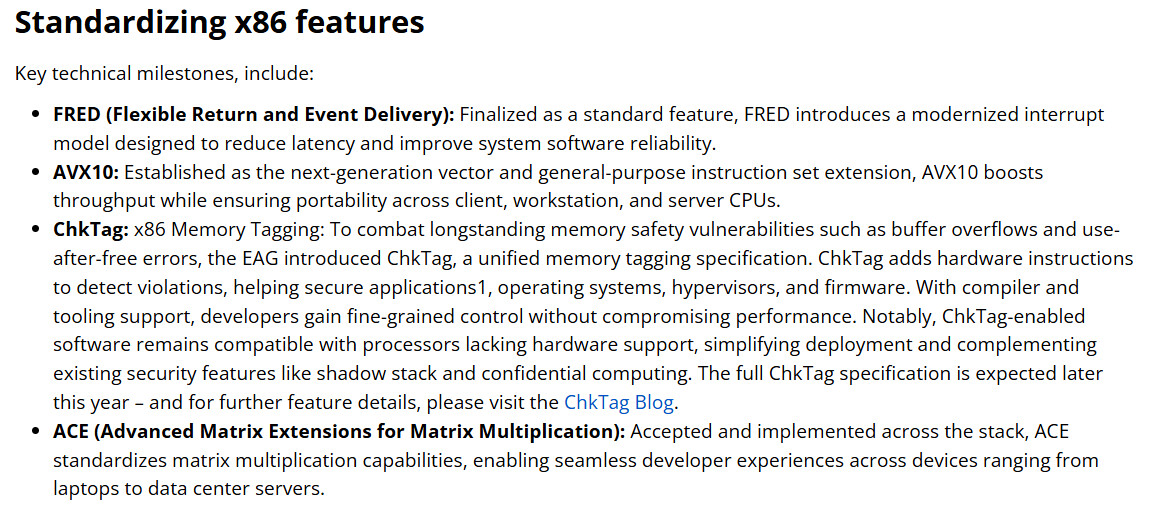

AMD wspomniało też o Zen 7, który wprowadzi nowy silnik macierzowy i większą ilość obsługiwanych instrukcji, w tym niezwykle przydatne AVX10 i ACE (Advanced Matrix Extensions for Matrix Manipulation). W Zen 7 zostanie też zaimplementowany nowy model zarządzania pamięcią o nazwie FRED (flexible return and event delivery), a także ChkTag x86 Memory Tagging, co ma zmniejszyć opóźnienia w przesyle danych.

|

| |

|

|

|

|

|

|

|

|

|

|

K O M E N T A R Z E |

|

| |

|

- @Wedelek (autor: Conan Barbarian | data: 12/11/25 | godz.: 19:45)

6Ghz -> 6 GHz

Straszne jest to sranie na poprawność techniczną a przecież TPC to technologiczny portal.

- @Conan (autor: Wedelek | data: 12/11/25 | godz.: 19:52)

nie przesadzasz trochę? zwykła literówka - poprawione.

- @up (autor: Conan Barbarian | data: 12/11/25 | godz.: 20:02)

Zwykła literówka to jest w qrwa, tutaj to jest sabotaż techniczny.

- oczekuję (autor: Zbyszek.J | data: 13/11/25 | godz.: 22:27)

około 30-40% wzrostu wydajności na rdzeń - liczonej jako suma wzrostu IPC i wzrostu częstotliwości taktowania.

Wszystko poniżej będzie rozczarowaniem i porażką, zwłaszcza uwzględniając fakt, że z ZEN 5 do ZEN 6 jest przeskok o dwie generacje litografii - tj z 5nm/4nm, przeskakują odrazu do 2nm z pominięciem litografii 3nm.

Wzrost IPC musi być minimum 15-16% - ZEN 5 to była całkiem świeża architektura, która jednak tylko niewiele przegoniła ZEN 4 we wskaźniku IPC, ale ma w tym zakresie duże pole do dalszej optymalizacji.

- @news (autor: Promilus | data: 14/11/25 | godz.: 05:22)

Jak ja uwielbiam te "AI coś tam" ... gówno nie AI. Na uj to komu w zwykłych rdzeniach, od tego jest grafika albo dedykowany układ, który zrobi kółka wokół takiego ZEN7 z fp8. Chcą consumer CPU to niech walczą o wydajność w grach i programach które wykorzystuje konsument detaliczny.

- @4. (autor: Mariosti | data: 14/11/25 | godz.: 14:33)

Intel przez lata uzyskiwał 3-5% wzrostu IPC z generacji na generację i jakoś zachwyty były nad jego procesorami, a jak AMD miałoby zejść w okolice 10% przy n razy większym skomplikowaniu architektury to już miałaby być porażka?

Wielki przeskok w procesie produkcji na logikę może wiązać się właśnie z niewielkim wzrostem IPC, wzrostem taktowania, a wzrostem IPC w kolejnej generacji w podobnym/tym samym procesie.

Jak AMD zrobi przy okazji takiego przeskoku procesu i istotny wzrost IPC i taktowania to w skali intela będzie to rewolucja na skalę dekady.

- powiedzmy że może być dość imponująco, (autor: Qjanusz | data: 14/11/25 | godz.: 23:55)

ale nie tak jak wróżby Zbyszka. No gdzie 30-40% wzrostu wydajności na rdzeń? Nie ma takiej opcji z generacji na generację

ChkTag - brzmi dość dobrze, zwłaszcza w kontekście budowy chipletowej

- Zbyszek.J (autor: PCCPU | data: 16/11/25 | godz.: 04:17)

Zen5 vs Zen4:

Średnia wzrostu IPC +16% do 35%.

Średnia INT +13% i średnia FP +25%.

Średnia dla AVX512 +56%.

Część obszaru dzięki lepszemu procesowi pójdzie na więcej rdzeni na CCD(12C/24T) i cache L3 48MB. Ale dalsze optymalizacje i rozbudowa logiki rdzeni x86 w Zen6 też będzie ;)

Myślę że śmiało można oczekiwać dla Zen6 średnią krzywej wzrostu IPC około 15%.

- Qjanusz (autor: PCCPU | data: 16/11/25 | godz.: 04:25)

Tak, Zen6 może odnotować wzrost IPC +30-40%, ale będzie to blisko górnej granicy krzywej.

Wielu zapomina, że ​​nie ma czegoś takiego jak liniowy wzrost IPC dla całego spektrum obciążeń/aplikacji.

Na przykład Zen5 ma krzywą wzrostu IPC od +10% do +35%, ze średnią +16% (bez uwzględnienia AVX512).

- Zbyszek.J (autor: rainy | data: 16/11/25 | godz.: 11:10)

W takim razie już powinineś przygotowywać się na rozczarowanie, ponieważ takiego wzrostu nie będzie.

Jeżeliby przyjąć wzrost zegara na poziomie około 10 procent, to żeby osiągnąć Twoje 30-40 procent przyrostu wydajności IPC musiałoby wzrosnąć o 20-30 procent, co nigdy nie miało miejsca od momentu debiuty architektury Zen (Zen 3 miał 19 procent).

Btw, moje przewidywania, to circa 10 procent wyższy zegar i wzrost IPC w przedziale 10-15 procent.

- @Rainy (autor: PCCPU | data: 16/11/25 | godz.: 11:47)

Jestem w stanie dać wiarę że będzie przy jakimś typie obliczeń i zastosowaniu. Ale nie będzie to średnia z całego spektrum krzywej wzrostu IPC.

Zen6 ma otrzymać m.in dodatkowe pory wykonawcze głównie dla AI/AVX512 co może dać większy wzrost w danych przypadkach obliczeń.

Także ja przewiduję krzywą wzrostu IPC od np +5% do 30-40% z średnią +~13%-15%.

- Edit: (autor: PCCPU | data: 16/11/25 | godz.: 11:51)

Myślę że to bezpieczne założenie i typowe dla ulepszeń generacyjnych Zen. Jak jeszcze dojdzie do tego wyraźnie wyższe taktowanie to będzie na prawdę dobrze :)

Ostatnio dużo spędzam czasu na porównywaniu Zen5 do P core M5 i dochodzę do bardzo ciekawych wniosków(nawiasem mówiąc) :)

- Dodam (autor: PCCPU | data: 16/11/25 | godz.: 17:11)

To że marketingowa krzywa wzrostu IPC dla Zen5 zaczyna się od +10% a kończy na +35% w ubranym zestawie testów nie znaczy że nie ma zastosowań w których będzie tylko +3-5% czy więcej niż +35% ;)

- Zen (autor: PCCPU | data: 16/11/25 | godz.: 17:15)

Krzywa wzrostu Zen3 miała rozpiętość od +9 do +39% (średnia +19%)

Krzywa wzrostu Zen4 miała rozpiętość od +1 do +39% (średnia +13%)

- Także (autor: PCCPU | data: 16/11/25 | godz.: 17:26)

Sugeruje bardzo chłodne podejście ponieważ projektowanie rdzeni jest coraz trudniejsze przy tym trzeba brać pod uwagę wiele różnych czynników i balansować między złożonością a faktycznym zyskiem.

Wielu porównuje współczesne x86-64 do P Core Mx bez zastanowienia, bez analizy mikro architektury itd ;)

- Mx APPLE (autor: PCCPU | data: 16/11/25 | godz.: 18:00)

Co do Mx (Apple) P Core to nie wszystko złoto co się świeci. Całkiem inne podejście bez op cache(który przy ARM nie ma sensu) inny model programowy rdzeni i przetwarzanie instrukcji. X86(1-15 Bajtów) kilku krotnie bardziej złożone instrukcje względem ARM(4 Bajty) ale pełna elastyczność i szczytowo dekoder Zen5 jest w stanie mieć wiekszą przepustowość w skomplikowanych instrukcjach. ARM ma dobre zyski przy prostych instrukcjach ale i tak bardziej złożone robi za pomocą kilku instrukcji a x86 może podxielić jedną skomplikowaną na kilka prostych i wykonać równolegle.

Jedna z analiz

Zen5

Symetryczne 4xAGU(4xLoad/Store)(4xLoad lub 2xLoad + 2xStore)) przepustowość szczytowo ~1,5TB/s

LionCove

6xAGU(3xLoad + 3xStore)

M5 P-Core

4xAGU(2xLoad, 1xLoad/Store i 1xStore) przepustowość szczytowo ~1TB/s

- To tylko drobny z aspektów (autor: PCCPU | data: 16/11/25 | godz.: 18:25)

Zen5 pobiera z L1-I 2x32Bajty na cykl(64Bajty na cykl)

M5 P-Core z L1-I 32Bajty na cykl

Nie wielu zdaje sobie sprawę że ma pod nosem tak zaawansowany i skomplikowany rdzeń jak Zen5. Ja patrzę na Zen5 przez pryzmat całego spektrum zastosowań-typów obliczeń/kodu a moc obliczeniowa jest ogromna i przepustowość wewnętrzna pojedynczego rdzenia liczona jest nawet w TB/s.

To coś niesamowitego mieć miżliwość obcowania z tak zaawansowaną technologią. Cieszę się z powrotu do AMD i Zen5 :)

- @CD (autor: PCCPU | data: 16/11/25 | godz.: 18:37)

Zen5

L3 32MB, 47 cykli, ST 173.6GB/s, nT 1.6TB/s(9900X 2x6C,2x 32MB L3)

LionCove

L3 36MB, 84 cykle, ST 57GB/s, nT ~1TB/s(285K)

- @CD (autor: PCCPU | data: 16/11/25 | godz.: 18:44)

Jestem bardzo dobrej myśli co do Zen6 i Zen7 :) Jest na co czekać i nie będziecie zawiedzeni ;)

- Zen6 (autor: PCCPU | data: 17/11/25 | godz.: 11:54)

Jakie zmiany mogą zajść w Zen6:

Możliwe że L1-I 48KB 12-Way, ulepszony i tak już bardzo rozbudowany i skomplikowany BPU i większe bufory BTB(Zen5 już ma ogromne), większy op cache, szerszy renamer(10-Wide) ponieważ obecnie ma 8-Wide co ogranicza szeroki op cache 6K 12-Wide. Zen5 w bardzo dużej części korzysta z przepustowości op cache a dużo mniej z szerokości dekodera co skłoniło inżynierów do pozostawienia dla ST jednego klastra dekodera 4-Wide. Drugi klaster dekodera jest głównie do specyficznych sytuacji i SMT. Możliwe że Zen6 zyska 5AGU(5xLOAD/STORE) itd

- @CD (autor: PCCPU | data: 17/11/25 | godz.: 14:03)

Większy ROB 500+, większe schedulery i więcej potoków FPU itd.

- @CD2 (autor: PCCPU | data: 17/11/25 | godz.: 17:40)

ROB 560+

- @PCCPU (autor: Wedelek | data: 20/11/25 | godz.: 21:05)

oby tylko w tej całej bańce AI ceny nie odjechały w kosmos.

PS: aleś tych komentarzy wygenerował ;)

- @5. (autor: pwil2 | data: 19/12/25 | godz.: 18:41)

AI na procesorze ma dostępne dużo więcej pamięci.

48MB L3 może dość dużo dać w grach już w podstawowym modelu.

IPC może wzrosnąć i 10%, ale jeśli 12c w 2nm będzie trzymać wysokie taktowania, mając wspólne 48MB cache to może być całkiem ciekawie w wymagających grach.

Ryzen 9600/X ostatnio jakoś dostał kopa w nowszych grach względem 7500F.

|

|

|

|

|

|

|

|

|

D O D A J K O M E N T A R Z |

|

| |

|

Aby dodawać komentarze, należy się wpierw zarejestrować, ewentualnie jeśli posiadasz już swoje konto, należy się zalogować.

|

|

|

|

|

|

|

|

|

|