|

TwojePC.pl © 2001 - 2026

|

|

Środa 4 lutego 2026 |

|

| |

|

AMD prezentuje nową rodzinę układów FPGA Kintex UltraScale+ Gen 2

Autor: Wedelek | źródło: AMD | 05:58 |

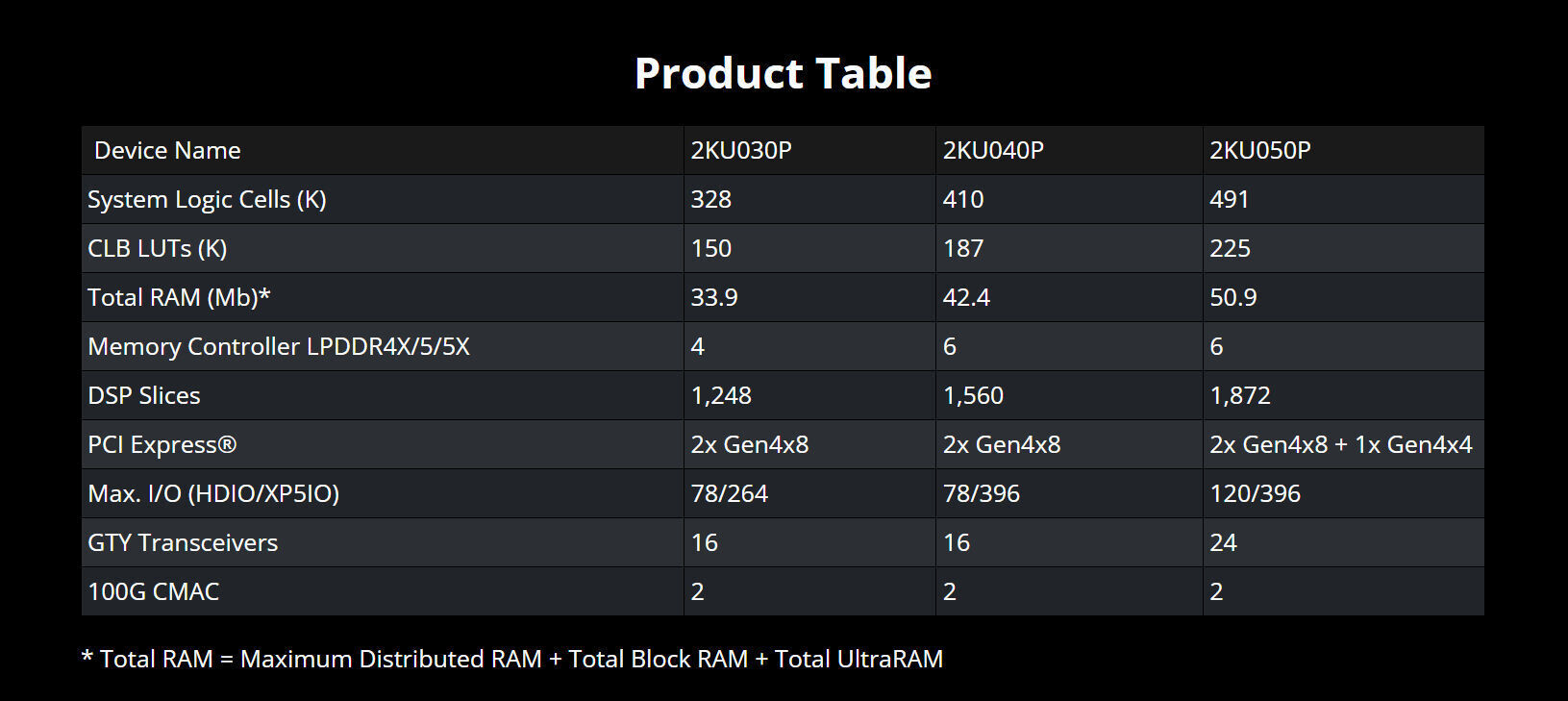

(3) |  AMD ogłosiło nową rodzinę programowalnych płytek FPGA Kintex UltraScale+ Gen 2. Nowa rodzina ma za zadaniem rywalizować z układami Intel Agilex 5 i być skierowana do branż wymagających długoterminowej niezawodności, jak obrazowanie medyczne, automatyka przemysłowa czy produkcja wideo na żywo. Nowa seria to głęboka modernizacja 16 nm platformy Kintex zaprojektowanej przez Xilinxa jeszcze przed przejęciem tej firmy przez AMD. AMD ogłosiło nową rodzinę programowalnych płytek FPGA Kintex UltraScale+ Gen 2. Nowa rodzina ma za zadaniem rywalizować z układami Intel Agilex 5 i być skierowana do branż wymagających długoterminowej niezawodności, jak obrazowanie medyczne, automatyka przemysłowa czy produkcja wideo na żywo. Nowa seria to głęboka modernizacja 16 nm platformy Kintex zaprojektowanej przez Xilinxa jeszcze przed przejęciem tej firmy przez AMD.

Najważniejsze ulepszenia dokonano w podsystemie pamięci, który bazuje teraz na modułach LPDDR4X, DDR5 i LPDDR5X (zamiast DDR4). Pojawiły się też nowe interfejsy I/O, w tym PCI-Express Gen 4 (zamiast Gen 3) oraz dual 100G Ethernet MAC, a także wsparcie dla LUT6 logic (vs LUT4 u Lattice Avant) i kryptografii CNSA 2.0. Zbudowane na bazie tej samej litografii co poprzednik układy (16 nm od TSMC) pracują z wyższą częstotliwością i mają oferować wyższą efektywność energetyczną.

AMD zapowiedziało udostępnienie wsparcia dla narzędzi Vivado/Vitis w Q3 2026, próbki inżynieryjne mają być dostępne do końca 2026 roku, a masowa produkcja ruszy w pierwszej połowie 2027 r.

|

| |

|

|

|

|

|

|

|

|

|

|

K O M E N T A R Z E |

|

| |

|

- @news (autor: Promilus | data: 4/02/26 | godz.: 18:43)

Agilex ma HPS z wielordzeniowym ARM w określonych modelach, Kintex nic nie będzie miał? To trochę słabo, bo to żadna rywalizacja na tym samym polu.

- @1. (autor: Mariosti | data: 6/02/26 | godz.: 09:28)

Szczerze to nie wiem czy to zaleta łączenie FPGA z ARM'em.

FPGA ma na sobie w zasadzie zawsze zamknięty soft, wyspecjalizowany, mocno zoptymalizowany i rzadko zmieniający się.

Przejście na nowe FPGA to masa tej roboty od nowa - ogromne koszty.

Jednocześnie ARM rozwija się dość sprawnie, a na nim działa sobie zwykle jakiś LFS, którego aktualizacje to w większości zaciągnięcie nowych źródeł z otwartych repo i puszczenie regresji na CI (jak są oczywiście kompleksowe testy napisane).

Także wysiłek potrzebny na 1 update hw FPGA, można zwykle przeznaczyć na zaktualizowanie LFS'a i zmianę hw ARM co najmniej 10 razy.

Zapewne istnieją jakieś ultra specyficzne zastosowania będące wyjątkami od tej zasady... ale generalnie tak jak z własnego doświadczenia wiem jak fpga jest używane w różnych produktach w których ASICi nie wchodzą w grę, bo mimo iż kod na FPGA nie zmienia się za często, to jednak zmienia się i kategorycznie musi mieć taką możliwość aby produkt miał jakąkolwiek wartość.

Także łączenie FPGA i ARM w jeden chip wydaje się bez sensu. U nas są na jednym PCB, ale dzięki relatywnie łatwo jest zaprojektować nową wersję PCB z tym samym FPGA i z nowym ARM'em.

- @mariosti (autor: Promilus | data: 6/02/26 | godz.: 16:53)

Łączenie CPU z FPGA od dawna było celem obu producentów, tak wyglądały niektóre Cyclone V m.in. oraz np. ZynQ or Xilinx. Wcześniej były rdzenie PowerPC. Po co to jest? Softcore na FPGA jest zazwyczaj relatywnie słaby (wolny) a zużywa dużo zasobów. Jak się chce odpalić coś co jednocześnie będzie miało szybko działający soft i responsywne I/O z opcją softcore dsp mielącego w czasie rzeczywistym duże ilości danych to zasadniczo łatwiej to zrobić na SoC FPGA niż próbując coś łatać z 2 układów z wykorzystaniem PCIe o relatywnie dużych opóźnieniach. A koszt HPS w FPGA jest stosunkowo mały więc jest to też oszczędność pieniędzy.

|

|

|

|

|

|

|

|

|

D O D A J K O M E N T A R Z |

|

| |

|

Aby dodawać komentarze, należy się wpierw zarejestrować, ewentualnie jeśli posiadasz już swoje konto, należy się zalogować.

|

|

|

|

|

|

|

|

|

|