|

TwojePC.pl © 2001 - 2026

|

|

Czwartek 20 czerwca 2024 |

|

| |

|

Intel podał szczegóły swojej litografii "Intel 3"

Autor: Zbyszek | źródło: Intel | 17:20 |

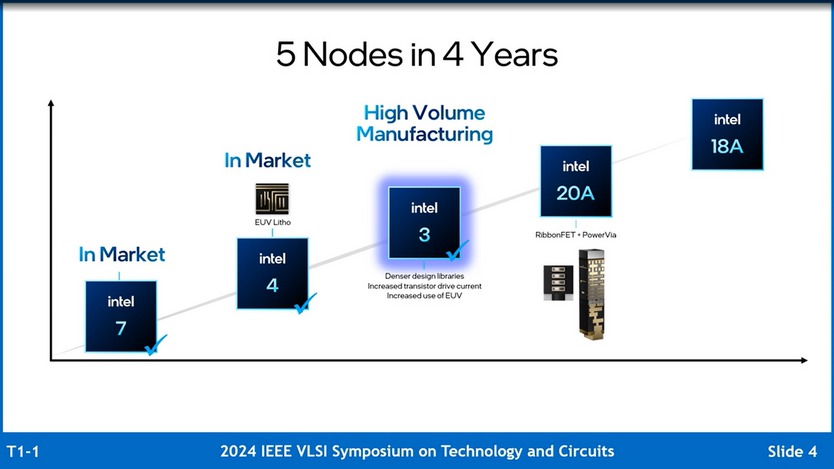

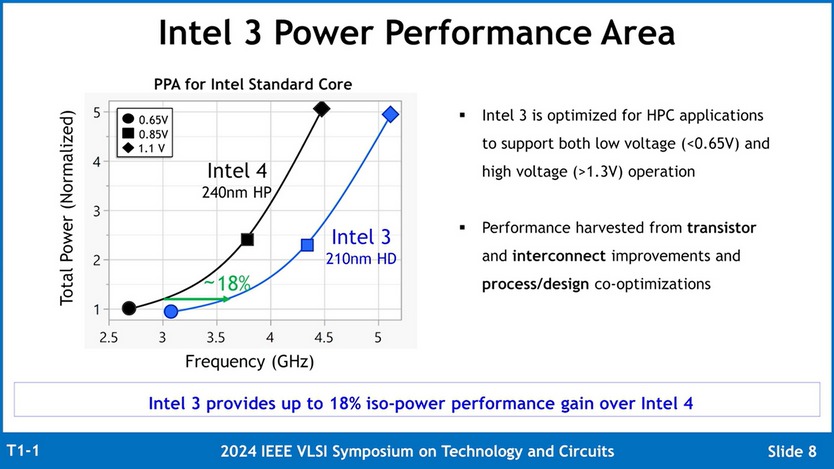

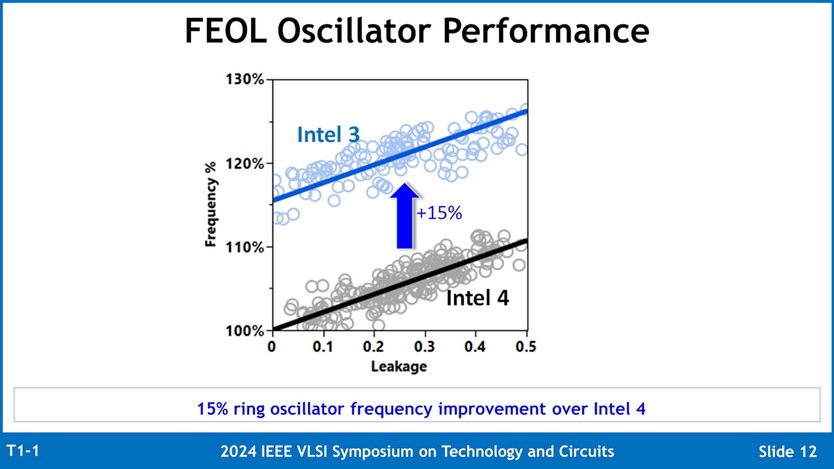

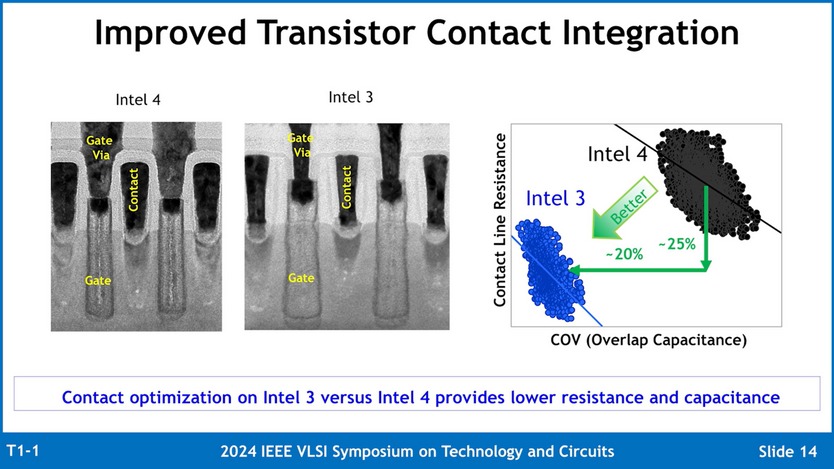

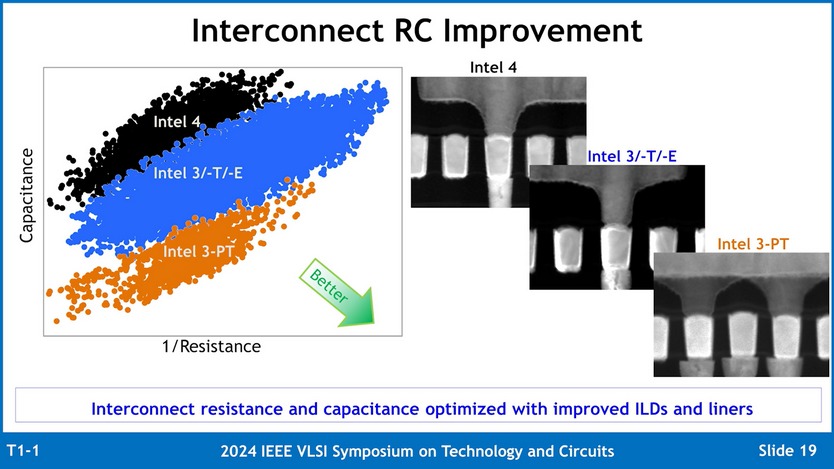

(19) |  Podczas konferencji naukowej organizowanej przez IEEE Intel podał szczegóły swojej nowej litografii o nazwie "Intel 3". Proces produkcyjny był wcześniej określany jako ulepszona wersja litografii "Intel 4" stosowanej w mobilnych procesorach Meteor Lake, ale teraz o litografii "Intel 3" wiemy więcej szczegółów. Względem litografii "Intel 4", nowy proces litograficzny oferuje o 18 procent zwiększoną wydajność tranzystorów. Toleruje też nieco niższe i nieco wyższe napięcia zasilające, oraz pozwala wytwarzanym układom scalonym na uzyskiwanie o około 0,5 GHz wyższej częstotliwości taktowania, względem tego gdyby były wyprodukowane w litografii "Intel 4". Podczas konferencji naukowej organizowanej przez IEEE Intel podał szczegóły swojej nowej litografii o nazwie "Intel 3". Proces produkcyjny był wcześniej określany jako ulepszona wersja litografii "Intel 4" stosowanej w mobilnych procesorach Meteor Lake, ale teraz o litografii "Intel 3" wiemy więcej szczegółów. Względem litografii "Intel 4", nowy proces litograficzny oferuje o 18 procent zwiększoną wydajność tranzystorów. Toleruje też nieco niższe i nieco wyższe napięcia zasilające, oraz pozwala wytwarzanym układom scalonym na uzyskiwanie o około 0,5 GHz wyższej częstotliwości taktowania, względem tego gdyby były wyprodukowane w litografii "Intel 4".

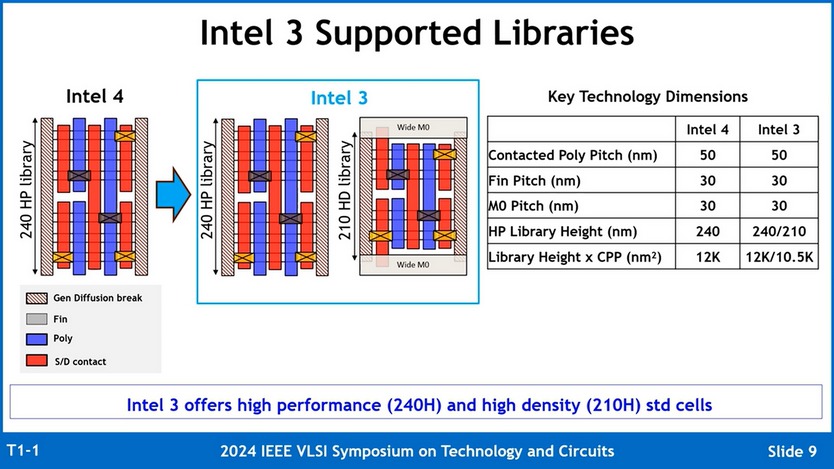

Litografia "Intel 3" przynosi też wzrost gęstości upakowania tranzystorów o 10 procent, jeśli do zaprojektowania obwodów użyte zostaną nowe biblioteki projektowe. Ewentualnie możliwe jest też wytwarzanie chipów o takiej samej gęstości upakowania tranzystorów jak w litografii "Intel 4" (przy użyciu starszych bibliotek).

Chociaż Intel tego nie stwierdził, to prawdopodobnie 18 procentowa poprawa wydajności tranzystorów dotyczy właśnie tego przypadku, gdy ich gęstość upakowania jest taka sama jak w przypadku litografii "Intel 4", a skorzystanie z możliwości zwiększenia gęstości upakowania tranzystorów o 10 procent powoduje lekki spadek ich wydajność.

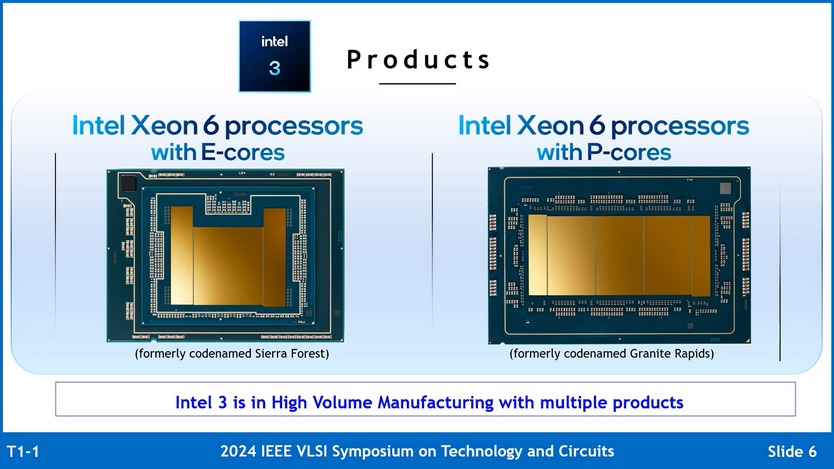

Pierwszymi procesorami wykorzystującymi proces litograficzny "Intel 3" będą nowe serwerowe Xeony 6. generacji z serii Sierra Forest i Granite Rapids

|

| |

|

|

|

|

|

|

|

|

|

|

K O M E N T A R Z E |

|

| |

|

- Ale jaka jest faktyczna technologia (autor: VP11 | data: 21/06/24 | godz.: 10:01)

Tak i nie podali. Dalej jadą na 10nm ?

Przecież to podstawa podać w jakiej technologii produkowane są chipy.

- te litografie (autor: Zbyszek.J | data: 21/06/24 | godz.: 11:37)

to prawdopodobnie odpowiedniki 5nm i 4nm od TSMC

- Z tego co pamiętam (autor: VP11 | data: 21/06/24 | godz.: 12:31)

To oni mocno odstają i aby lepiej wyglądać po prostu wymyślili sobie że ich pakowanie jest podobne do konkurencji w jakiejś tam technologii. Czyli mając 10nm mogą pisać Intel 3, No lepiej że wygląda Intel 3 niż intel 10. Ale po fakcie jest to oszustwo. Wtedy lepiej nic nie pisać.

Papier zniesie każde kłamstwo.

Chciałem wiedzieć czy oni zeszli do 5nm czy zaczynają przegrywać chińczykom w tym.

- up ... (autor: VP11 | data: 21/06/24 | godz.: 12:45)

Gdzieś piszą że to 5nm, w innym miejscu że to 7nm. No i też słyszałem, że po prostu wykorzystują mocy tych kto może drukować w 3nm. I też o tym piszą. A to już ciekawie się robi. Albo 3 albo 5 albo i 7 nm. Czarna magia skryta pod tym Intel 3.

Well it’s official, now Intel’s nm designation is copium. Intel 3 is classified as 5nm according to IEEE specifications with 50nm gate pitch and 30nm interconnect pitch. TSMC N3 actually beats IEEE specifications for 3nm at 48nm gate pitch and 23nm interconnect pitch.

Intel na targach Computex 2024 zaprezentował procesory Intel Xeon 6, które powstają przy wykorzystaniu procesu litograficznego Intel 3 (odpowiednik 7 nm).

w TSMC ruszyła właśnie masowa produkcja rodziny Lunar Lake. Co więcej, Intel zagarnął dla siebie większość mocy przerobowych w litografii 3 nm, zyskując przewagę nad AMD, NVIDIĄ i Qualcommem.

- VP11 (autor: Markizy | data: 21/06/24 | godz.: 17:09)

od podajże 28nm każdy kolejny rozmiar to jeden wielki kant pod względem faktycznej wielkości wiec o czym mi piszemy.

Istotne jest tylko to czy będzie lepszy od konkurecji

- ... Chwalą się procesem a lapki z nowymi procesorami mają obsuwę... (autor: SebaSTS | data: 22/06/24 | godz.: 15:53)

... Do września.

- według ich własnych materiałów to (autor: kombajn4 | data: 23/06/24 | godz.: 06:36)

10nm+EUV -> Intel 7

7nm -> Intel 4

(7nm?) "power and area inprovment" ->Intel 3

(??)"braklethroug technology" -> Intel 20A

przy czym ten ichni przełom w 2021 był wpisany na H1 2024

- czyli innymi słowy (autor: kombajn4 | data: 23/06/24 | godz.: 06:38)

są na etapie 7nm z usprawnieniami, czyli to co TSMC nazwało 6nm

- Nie jest tak jak piszesz (autor: Shark20 | data: 24/06/24 | godz.: 00:11)

Proces 14nm intela odpowiadał 14nm/12nm TSMC. Litografia 10nm intela to gęstość tranzystorow zwiększona nie o 2x, lecz 2,7x. To bardziej odpowiada 7nm lub raczej 8nm od TSMC.

Litografia Intel 7nm, czyli Intel 4 pod względem gęstości tranzystorow jest podobna do 5nm od TSMC. A Intel 3 wydaje sie być litografia podobną do 4nm od TSMC

- @09 (autor: kombajn4 | data: 24/06/24 | godz.: 20:16)

Obawiam się że gdyby było tak jak mówisz to procesory Intela nie pożerałyby tak absurdalnych ilości prądu

- kombajn4 (autor: Markizy | data: 25/06/24 | godz.: 18:43)

to może wynikać z samego projektu rdzenia. Proces jest rzeczą istotną ale projekt rdzenia ma też duże znaczenie. Przykład masz llano i buldożer.

- Zużycie energii układów obliczeniowych na mm2 i na tranzystor cały czas rośnie. (autor: Mario1978 | data: 27/06/24 | godz.: 15:11)

Z generacji na generacje jest co raz wyższy przy czym można go obniżyć stosując najnowszą litografię produkcji z mniejszym zagęszczeniem tranzystorów na mm2. Firmy takie jak Intel zaczęły to nazywać jako Ultra Wydajność. Czyli robiąc większe przerwy między tranzystorami są w stanie wyciągnąć wyższą wydajność jednego wątku ale ten sposób nigdy nie będzie dobry tam gdzie mocy obliczeniowej nigdy za mało. Co z tego, że układ obliczeniowy ma potężne kilka wątków obliczeniowych jak potrzeba większej ilości operacji na wątkach wymusza spadek zegara taktującego rdzenie najszybsze. Dlatego u Intela jako jedynej firmy jak na razie maksymalna gęstość upakowania tranzystorów w przypadku układów, które chcą skorzystać z potężnego silnego wątku jest czasami poniżej 30% tego co prezentuje układ z wysoką gęstością tranzystorów. Teraz nawet TSMC specjalnie dla takich firm jak Nvidia czy AMD wprowadził po raz pierwszy tranzystory o maksymalnej wydajności i pierwszym takim przykładem jest litografia N4X, z której jeszcze nikt nie korzysta. Zapowiada się, że Strix Halo właśnie coś takie dostanie. Ale bardziej interesująće są testy jak Intel dalej próbuje oszukiwać ludzi na TDP. Nie będę nawet zdziwiony gdy Lunar Lake z TDP 17W od Intela będzie miał taki sam pobór energii jak Strix Point z TDP 45W. A jak Strix Point będzie mieć TDP 32W od AMD to LL od Intela przy TDP 17W będzie pobierał od niego więcej energii.

- @12. (autor: Mariosti | data: 27/06/24 | godz.: 19:21)

Nieprawda, na tranzystor zużycie energii ciągle spada, względem mocy obliczeniowej też.

Na mm2 rośnie ale to naturalna konsekwencja coraz mniejszych tranzystorów i jest ciągle wiele lepszych technik chłodzenia rdzenia które jeszcze nie są konieczne dla klienta masowego, ani dla enterprise.

- Mariosti (autor: Markizy | data: 28/06/24 | godz.: 07:00)

a jakie to lepsze techniki chłodzenia mamy jeszcze do wyboru? Z tego co wiem głównym problem jest odebranie dużej ilości ciepła z tak małej powierzchni, wiec chciałbym wiedzieć jak sobie z tym poradzili.

Dlatego układy z komorami parowymi wszelkiego rodzaju są użytkowane, przechwytują ciepło szybciej niż metale.

- @13. (autor: pwil2 | data: 28/06/24 | godz.: 08:18)

Na milimetr i czasem na tranzystor rośnie, bo to darmowy dla producenta wzrost wydajności. Mniejszy układ z większą marżą sprzeda.

Płaci za to klient (chłodzenie, zużycie energii).

- @14. (autor: Mariosti | data: 28/06/24 | godz.: 09:41)

Direct die air cooling,

die integrated vapor chamber,

Die integrated water-cooling cold plate.

Są publikacje z testów tych rozwiązań i ostatnie jest jeszcze lata przed nami jeśli chodzi o faktyczną potrzebę jego wdrożenia.

- Mariosti (autor: Markizy | data: 28/06/24 | godz.: 22:40)

czyli mamy dwa stosowane rozwiązania i jedno opracowywane.

- @17. (autor: Mariosti | data: 29/06/24 | godz.: 08:50)

2 są stosowane w laptopach i w GPU, ale nie są stosowane w procesorach desktopowych gdzie masz największą moc na mm2.

- Mariosti (autor: Markizy | data: 29/06/24 | godz.: 10:57)

Direct die air cooling, nie jest stosowane ze względu na łatwość uszkodzenia rdzenia, ale za czasów athlonów i pentium iii było to popularne rozwiązanie. Ogólnie bezpieczniej dać czapkę i na nią dawać radiator pomimo tego że robi lekki opór termiczny ( i czapki potrafią być krzywo naklejone bądź być krzywe). Wszak procki serwerowe jak xeon i epic też mają czapki a tam zysk byłby dużo większy niż z niej nie korzystać.

Die integrated vapor chamber każdy Heatpipe jest taką komorą wiec jest to stosowne (osobna jest rozmowa o kształcie komory, ale samo chłodzenie też jest). To że nie jest to stosowane jako duża płaska powierzchnia wynika z ograniczeń w okół procesora. Przy am5 testowano zastosowanie vapor chamber jako IHS ale ich wewnętrzne testy nie pokazały znaczących korzyści poza wzrostem ceny.

https://www.techpowerup.com/...sign-for-zen-4-cpus

I jak widać każde rozwiązanie było w stacjonarkach lub w nich jest. Poza nie zrealizowanym die integrated water-cooling cold plate nie ma żadnych efektywniejszych alternatyw.

|

|

|

|

|

|

|

|

|

D O D A J K O M E N T A R Z |

|

| |

|

Aby dodawać komentarze, należy się wpierw zarejestrować, ewentualnie jeśli posiadasz już swoje konto, należy się zalogować.

|

|

|

|

|

|

|

|

|

|